### **Op-Amp/Comparator Application Note**

# **Operational amplifier , Comparator (Tutorial)**

This application note explains the general terms and basic techniques that are necessary for configuring application circuits with op-amps and comparators. Refer to this note for guidance when using op-amps and comparators.

### **Contents**

| 1 | Wh   | at Is Op-Amp/Comparator?                                                              | 2  |

|---|------|---------------------------------------------------------------------------------------|----|

|   | 1.1  | What is op-amp?                                                                       | 2  |

|   | 1.2  | What is comparator?                                                                   | 3  |

|   | 1.3  | Internal circuit configuration of op-amp/comparator                                   | 4  |

| 2 | Abs  | solute Maximum Rating                                                                 | 5  |

|   | 2.1  | Power supply voltage/operating range of power supply voltage                          | 5  |

|   | 2.2  | Differential input voltage                                                            | 6  |

|   | 2.3  | Input common-mode voltage                                                             | 7  |

|   | 2.4  | Input current                                                                         | 8  |

|   | 2.5  | Operating temperature range                                                           | 8  |

|   | 2.6  | Maximum junction temperature, storage temperature range                               | 8  |

|   | 2.7  | Power dissipation (total dissipation)                                                 | g  |

| 3 | Ele  | ctrical Characteristics                                                               | 10 |

|   | 3.1  | Supply current                                                                        | 10 |

|   | 3.2  | Input offset voltage                                                                  | 12 |

|   | 3.3  | Input bias current and input offset current                                           | 16 |

|   | 3.4  | Input common-mode voltage range                                                       | 18 |

|   | 3.5  | Maximum output voltage (High/Low level output voltage                                 | 20 |

|   | 3.6  | Large signal voltage gain (open loop gain)                                            | 22 |

|   | 3.7  | CMRR (Common Mode Rejection Ratio)                                                    | 23 |

|   | 3.8  | PSRR (Power Supply Rejection Ratio)                                                   | 27 |

|   | 3.9  | SR (Slew Rate)                                                                        | 30 |

|   | 3.10 | Frequency characteristics of op-amp                                                   | 31 |

|   | 3.11 | Phase delay and oscillation                                                           | 33 |

|   | 3.12 | Cause of phase delay in op-amp                                                        | 35 |

|   | 3.13 | Stability confirmation method (amplifier circuit)                                     | 36 |

|   | 3.14 | Stability confirmation method (unity feedback circuit/voltage follower)               | 37 |

|   | 3.15 | Summary of stability confirmation method                                              | 38 |

|   | 3.16 | Countermeasures against oscillation by load capacitance (output isolation resistor 1) | 38 |

|   | 3.17 | Countermeasures against oscillation by load capacitance (output isolation resistor 2) | 39 |

|   | 3.18 | THD+N (Total Harmonic Distortion + Noise)                                             | 40 |

|   | 3.19 | Input referred noise                                                                  | 44 |

|   | 3.20 | Response time (rise/fall times and propagation delay time)                            | 48 |

| 4 | Reli | iability Items                                                                        | 50 |

|   | 4.1  | Electrostatic Breakdown Voltage (ESD Breakdown Voltage)                               | 50 |

|   | 4.2  | Latch Up Test                                                                         | 51 |

|   |      |                                                                                       |    |

### 1 What is Op-Amp/Comparator?

### 1.1 What is op-amp?

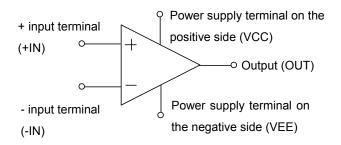

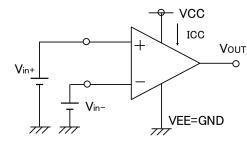

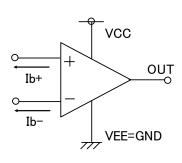

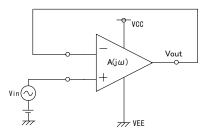

An op-amp (operational amplifier) is a differential amplifier that has high input resistance, low output resistance, and high open loop gain. Its function is to amplify the differential voltage between the + input terminal (non-inverting terminal) and the - input terminal (inverting terminal).

Each op-amp circuit is composed of five terminals: a power supply terminal on the positive side, a power supply terminal on the negative side, a + input terminal, a - input terminal, and an output terminal. (There are no general terms for the terminals except classifications such as power source, input and output.)

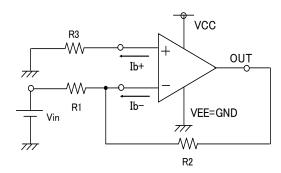

Figure 1.1.1. Op-amp/comparator symbol

Table 1.1.1. Examples of names for op-amp power supply terminals

|                                            | Bipolar type | CMOS type |

|--------------------------------------------|--------------|-----------|

| Power supply terminal on the positive side | VCC          | VDD       |

| Power supply terminal on the negative side | VEE          | VSS       |

Providing high input resistance (impedance) and low output resistance is a function required for the op-amps.

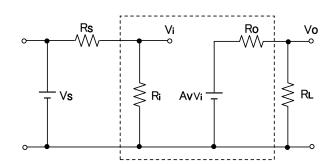

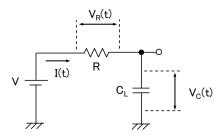

In Figure 1.1.2. Model of voltage controlled voltage source amplifier (op-amp),  $V_S$  is the input signal source,  $R_S$  is the signal source output resistor,  $R_i$  is the input resistor of the op-amp,  $R_O$  is the output resistor of the op-amp,  $R_L$  is the load resistor, and  $A_V$  is the amplification factor of the op-amp. The relation between the input and output voltages is described in the equation (1.1.1).

$$V_{O} = \frac{R_{i}}{R_{i} + R_{s}} V_{S} \times A_{V} \frac{R_{L}}{R_{O} + R_{L}}$$

(1.1.1)

As shown in Figure 1.1.2 and the equation (1.1.1), the signal voltage  $V_S$  is divided into resistance voltages by the signal source resistor  $R_S$  and the input resistor  $R_i$  of the op-amp. As a result, the input signal to the op-amp is attenuated. However, when the  $R_i$  is sufficiently larger than the  $R_S$  ( $R_i = \infty$ ), the first term in the equation (1.1.1) can be approximated by 1 and it can be considered that  $V_S = V_i$ . Next, as for the second term, the amplified input voltage  $A_VV_i$  is divided by the output resistor  $R_O$  of the op-amp and the load resistor  $R_L$  and output in Figure 1.1.2.

Here, the signal can be output without being attenuated if the  $R_{\text{O}}$  is sufficiently smaller than the  $R_{\text{L}}$  ( $R_{\text{O}}$ =0) because the second term can be approximated by 1. Such an op-amp is called an ideal op-amp. Usually, op-amps with high input resistance and low output resistance are preferred. The circuit configuration is designed to achieve an ideal op-amp as closely as possible.

Figure 1.1.2. Model of voltage controlled voltage source amplifier

Table 1.1.2. Ideal input and output resistances required for op-amp

|                                                        | Input resistance | Output resistance |

|--------------------------------------------------------|------------------|-------------------|

| Ideal op-amp<br>(Voltage controlled<br>voltage source) | 8                | 0                 |

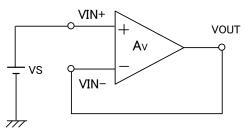

An op-amp amplifies a small differential voltage between the + input terminal and - input terminal and outputs the amplified voltage. For this purpose, an op-amp with a large amplification factor is preferred. The reason is explained using the voltage follower circuit in Figure 1.1.3.

A voltage follower circuit is a circuit in which the input and output voltages are equal. It is mainly used as a voltage buffer.

This circuit provides characteristics such as high input resistance and low output resistance, as mentioned above.

In Figure 1.1.3, the input voltage  $V_{\rm S}$  and the  $V_{\text{OUT}}$  become identical.

Figure 1.1.3. Voltage follower circuit

Since the op-amp amplifies the differential voltage between the terminals by the amplification factor of the op-amp, the output voltage is expressed with the equation (1.1.2).

$$V_{OUT} = A_V \times (V_{IN+} - V_{IN-}) = A_V \times (V_S - V_{OUT})$$

(1.1.2)

The equation (1.1.2) is converted to the equation (1.1.3).

$$\frac{V_{OUT}}{A_V} = V_S - V_{OUT} \tag{1.1.3}$$

In the equation (1.1.3), when the open loop gain of the op-amp is sufficiently high, the left side can be approximated by 0 and the equation gives  $V_S = V_{OUT}$ . When the gain is low, the left side of the equation (1.1.3) cannot be approximated by 0 and the output voltage will contain an error.

An op-amp with a high open loop gain is desirable because the error in the output voltage can be minimized by the high gain.

From another point of view, the high open loop gain means that the difference in the potentials between the + input terminal and the - input terminal is minimized. Namely, the higher the open loop gain is, the better the relation  $V_{\text{IN+}} = V_{\text{IN-holds}}$ . This relation in which the potentials of the + input terminal and the - input terminal become nearly equal is called a virtual short-circuit, imaginary short-circuit, or virtual

grounding. When configuring and using a negative feedback circuit, this relation is realized and application circuits are designed utilizing the characteristic of the virtual grounding.

### 1.2 What is comparator?

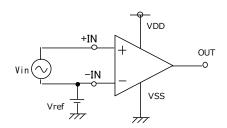

A comparator (voltage comparator) has the same terminal structure as an op-amp composed of five terminals: the + input terminal, the - input terminal, the positive side power supply terminal, the negative side power supply terminal, and the output terminal. When a comparator is used, the voltage is fixed at one of the input terminals as a reference terminal, and the difference between the reference voltage and the output voltage to the other terminal is amplified. The output voltage is either higher or lower than the reference voltage.

When the + input terminal potential > the - input terminal potential

→ High level output.

When the - input terminal potential > the + input terminal potential

→ Low level output.

The major difference between op-amps and comparators is whether or not the phase compensation capacitance exists. Since op-amps configure and utilize a negative feedback circuit, they require phase compensation capacitance to prevent oscillation inside the IC. On the other hand, since comparators will not configure the negative feedback circuit, they do not include the phase compensation capacitance. Since the phase compensation capacitance limits the response time between the input and the output, a comparator without the phase compensation capacitance provides a better responsiveness compared to an op-amp. In contrast, if an op-amp is used as a comparator, since the phase compensation capacitance limits the response, it provides a very poor responsiveness compared with a

Therefore, care must be taken when using an op-amp as a comparator.

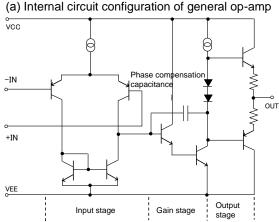

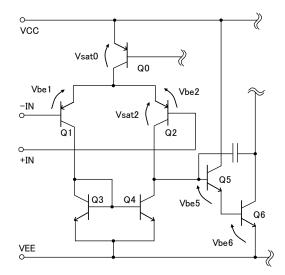

### 1.3 Internal circuit configuration of op-amp/comparator

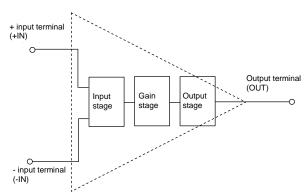

Figure 1.3.1 shows the internal circuit configuration of an op-amp. Generally, an op-amp is composed of three stages: the input stage, the gain stage, and the output stage.

The input stage is configured with a differential amplification stage that amplifies the differential voltage between the two terminals. In addition, it does not amplify the common-mode signal component (a condition where no difference in potential exists between the terminals and an equal voltage is input).

Since the gain is insufficient with the differential amplification circuit alone, the gain stage further increases the open loop gain in the op-amp.

In general op-amps, the phase compensation capacitance for oscillation prevention is connected over the gain stage.

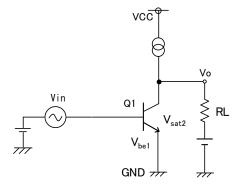

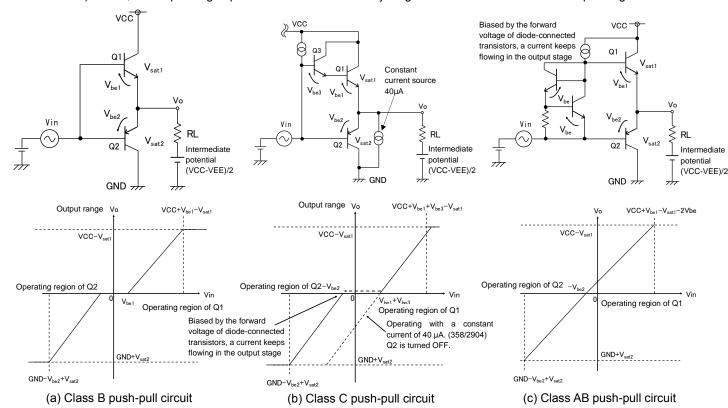

The output stage is connected as a buffer so that the op-amp characteristics will not be affected by loads such as the resistance connected to the output terminal. The changes in the output characteristics due to the loads (such as distortion or voltage drop) mainly depend on the circuit configuration and the current capability of the output stage. The type of output stage, Class A and B, C, or AB push-pull output circuit, is classified according to the amount of drive current flowing in the output circuit (the difference in the bias voltage).

+ input terminal (+IN)

Phase compensation capacitance

Output terminal (OUT)

- input terminal.

(a) Internal circuit configuration of general op-amp

(b) BA4558 Internal equivalent Figure 1.3.1. Internal circuit configuration of op-amp

The difference in the amount of drive current affects the distortion factor generated in the output stage. In general, the Class A output circuit has the lowest distortion factor, followed by Classes AB, B, and C.

Figure 1.3.2 shows the internal circuit configuration of a comparator. Although the circuit configuration is nearly identical to that of an op-amp, the phase compensation capacitance for oscillation prevention is not included in the comparator since it is not supposed to be used in a negative feedback configuration. Since the phase compensation capacitance limits the operating speed between the input and the output, the response time is remarkably better compared with op-amps.

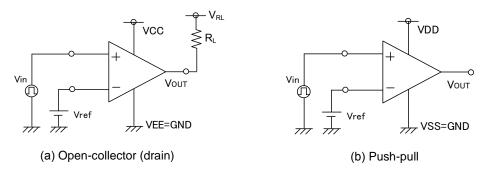

The type of output circuit for comparators is classified into the open collector (open drain) type or the push-pull type.

Figure 1.3.2 (b) shows the internal equivalent circuit of the BA2903. The BA2903 is an output circuit of the open collector type.

(a) Internal circuit configuration of general comparator

(b) BA2903 Internal equivalent

Figure 1.3.2. Internal circuit configuration of comparator

### 2 Absolute Maximum Rating

The absolute maximum rating is specified in the data sheet for op-amps/comparators. The absolute maximum rating provides the condition that must not be exceeded even instantaneously. The application of a voltage above the absolute maximum rating or use in a temperature environment outside the environment specified by the absolute maximum rating may cause the deterioration of characteristics or destruction of the internal circuit. The absolute maximum ratings for the following items are explained.

- Power supply voltage/operating range of power supply voltage

- 2.2. Differential input voltage

- 2.3. Input common-mode voltage

- 2.4. Input current

- 2.5. Operating temperature range

- 2.6. Maximum junction temperature, storage temperature range

- 2.7. Power dissipation (total dissipation)

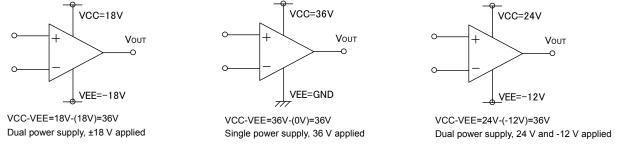

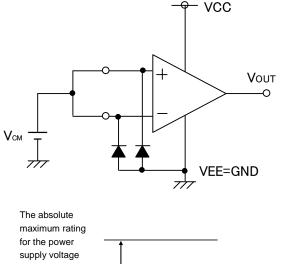

### 2.1 Power supply voltage/operating range of power supply voltage

For the power supply voltage, the absolute maximum rating refers to the maximum power supply voltage that can be applied between the positive side power supply terminal (VCC terminal) and the negative side power supply terminal (VEE terminal) of the op-amp without causing the deterioration of characteristics or destruction of the internal circuit. Figure 2.1.1 shows examples of the power supply voltage that can be applied to an op-amp/comparator that has an absolute maximum rating for the power supply voltage of 36 V. The absolute maximum rating for the power supply voltage specifies the difference in voltage between the VCC and VEE terminals. The op-amp/comparator must be used

with the value of (VCC-VEE) never exceeding the absolute maximum rating for the power supply voltage. Therefore, when 24 V and -12 V are applied to the VCC and VEE terminals, respectively, the difference in voltage between the terminals is 36 V and the deterioration of characteristics or destruction does not occur. It should be noted that the absolute maximum rating for the power supply voltage has a different meaning from the operating power supply voltage. The absolute maximum rating for the power supply voltage indicates the maximum value of the power supply voltage that will not cause the characteristics deterioration or destruction of the IC. It does not provide the voltage range in which the specifications and characteristics that are described in the data sheet are maintained. To obtain the characteristics that are guaranteed in the specifications, the op-amp/comparator must be used with the voltage value within the operating range of the power supply voltage. However, the absolute maximum rating for the power supply voltage of some products may be identical to the maximum value of the operating power supply voltage. Op-amps are sometimes called dual power supply or single power supply op-amps. In other words, an op-amp may be suited for the usage as a dual power supply or single power supply. Dual power supply op-amps have a voltage range in which either the input voltage or the output voltage cannot be output due to the circuit configuration on the positive power supply (VCC) side and the negative power supply (VEE) side. Therefore, the dual power supply op-amps are often used while applying a positive power supply and a negative power supply with the ground being the middle point. On the other hand, the single power supply op-amps are used while applying the positive power supply with reference to the ground and the input/output can be performed nearly at the ground level.

Figure 2.1.1. Examples of the power supply voltage that can be applied to an IC that has an absolute maximum rating for the power supply voltage of 36 V

Note: Dual power supply refers to the application of a power supply voltage to op-amps using two voltage power supplies (positive and negative). Single power supply refers to the application of a power supply voltage to op-amps with reference to the ground.

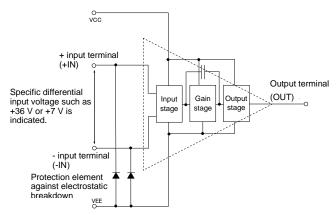

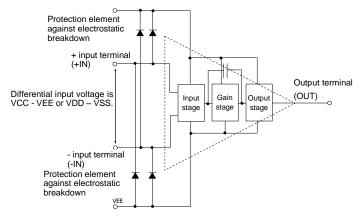

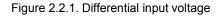

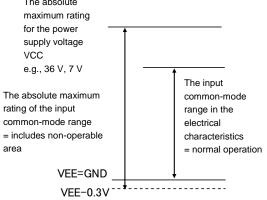

### 2.2 Differential input voltage

Differential input voltage indicates the maximum value of the voltage that can be applied between the + input terminal (non-inverting input terminal) and the - input terminal (inverting input terminal) without causing the characteristic deterioration or destruction of the IC. This voltage is the difference in voltage between the + input terminal and the - input terminal, and either of the terminals can be used as the reference. The polarity is not very important.

However, the potential of each input terminal is required to be higher than that of the VEE terminal. The reason for this requirement is that the current may flow out of the input terminal via the electrostatic protection element when the potential of the input terminal is lower than that of the VEE terminal, leading to deterioration or destruction.

Two types of protection element are available: the elements are connected between the input terminals and the VEE

(ground) as in Figure 2.2.1(a), or the elements are connected between the input terminals and both the VCC and VEE (ground) as in Figure 2.2.1(b).

In the former, since there is no current path on the VCC side, the differential voltage does not depend on the VCC value and is determined by factors such as the breakdown voltage of the transistors (e.g., NPN and PNP transistors) that are connected to the input terminals. In the latter, since a protection element is located on the VCC side as well and the potential of the input terminals must be lower than that of the VCC, the differential input voltage is determined by VCC - VEE or VDD - VEE. Some op-amps use an NPN differential input stage and the clamp diodes for the protection between the base and emitter of these transistors are connected between the input terminals. The differential voltage in such products may be specified to several volts (Figure 2.2.2).

(a) When the electrostatic protection element is located only on the VEE (ground) side

(potential of input terminal must be higher than that of VEE)

(b) When the electrostatic protection elements are located on both the VCC and VEE (ground)

(potential of input terminal must be higher than that of VEE and lower than that of VCC)

When the diodes for the overvoltage protection are connected between the + input terminal and the - input terminal Figure 2.2.2. Differential input voltage (with the protection between the terminals)

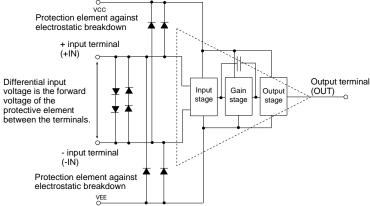

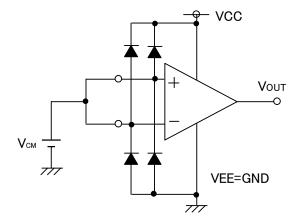

### 2.3 Input common-mode voltage

For the input common-mode voltage, the absolute maximum rating indicates the maximum voltage that can be applied without causing the characteristic deterioration or destruction of the IC when the potentials of the + input terminal and input terminal are set to the same value. Unlike the input common-mode voltage range in the electrical characteristics specifications, the absolute maximum rating for the input common-mode voltage does not guarantee the normal operation of the IC.

If normal operation of the IC is expected, the voltage must follow the input common-mode voltage range in the electrical characteristics items. Generally, the absolute maximum rating for the input common-mode voltage is -0.3 V and +0.3 V for the VEE and VCC, respectively. However, as mentioned in section 2.2 Differential input voltage, the voltage can be applied up to the absolute maximum rating for the power supply voltage (e.g., +36 V for the VEE) in some products in which the protection element is not present on the VCC side.

In summary, the input common-mode voltage is determined by the protection circuit configuration and the parasitic element of the input terminals as well as the breakdown voltage of the input transistors among other factors. Figure 2.3.1 shows the absolute maximum rating for the input common-mode voltage.

In addition, the value of 0.3 V indicated in "VEE-0.3V" or "VCC+0.3V" represents the voltage range in which the electrostatic protection elements (diodes) are not activated when the forward voltage is applied to the protective element. For the protection method when a voltage outside the input voltage range is applied, refer to the next section, 2.4 Input current.

When the electrostatic protection element is located only on the VEE (ground) side (VEE of -0.3 V to the absolute maximum rating for the power supply voltage)

Depends on the power supply voltage being used

When the electrostatic protection elements are located on both the VCC and VEE (ground) (VEE of -0.3 V to the working power supply voltage of +0.3 V)

Figure 2.3.1. Absolute maximum rating for the input common-mode voltage

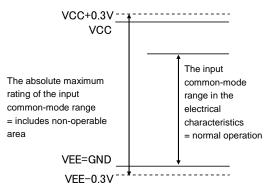

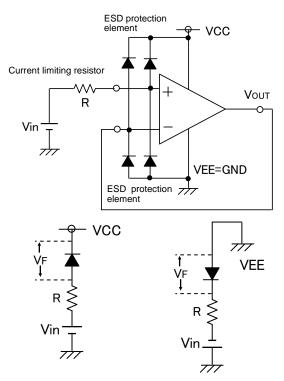

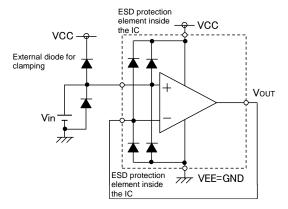

### 2.4 Input current

In sections 2.2 Differential input voltage and 2.3 Input common-mode voltage, it is explained that the current may flow into or out of the input terminals if a voltage is input at a value lower than the VEE of -0.3 V or higher than the VCC +0.3 V, leading to the characteristics deterioration or destruction.

As countermeasures, a small forward voltage diode for clamping can be provided on the input terminal, or the current flowing through the input terminal can be limited by inserting a resistor. The former is a method to limit the voltage that is input to the IC, while the latter is a method to limit the current. Set the resistor value so that the input current is 10 mA or less. Set the forward voltage of the diode ( $V_F$  in Figure 2.4.1) to approximately 0.6 V.

Figure 2.4.1. Connection of input current limiting resistor

Figure 2.4.2. Connection of input protection diode

### 2.5 Operating temperature range

Operation temperature range refers to the range in which the IC maintains the expected functions and operates normally.

The IC characteristics vary with temperature. Therefore, the standard values specified for 25°C are not necessarily guaranteed at other temperatures unless specified otherwise. There are some specification items that are guaranteed for all temperatures within the operating temperature range. The values for such items are standard ones that take into consideration the variation in IC characteristics within the operating temperature range indicated in the specifications. The data sheet lists the temperature characteristics data for the specification items. Refer to the data for using the IC.

### 2.6 Maximum junction temperature, storage temperature range

Maximum junction temperature is the maximum temperature at which the semiconductor can operate. The junction refers to the part where the chip and the package join. If the chip temperature exceeds the maximum junction temperature specified in the data sheet, a large number of electron-hole pairs will be generated in the semiconductor crystal, preventing the normal operation of the element. Therefore, the usage and thermal design should take into consideration the heat generation due to the power consumption by the IC and the ambient temperature. The maximum junction temperature is determined by the manufacturing process.

The storage temperature range indicates the maximum temperature of the storage environment when the IC is not operating, i.e., without consumption power. Usually, this value is the same as the maximum junction temperature.

### 2.7 Power dissipation (total dissipation)

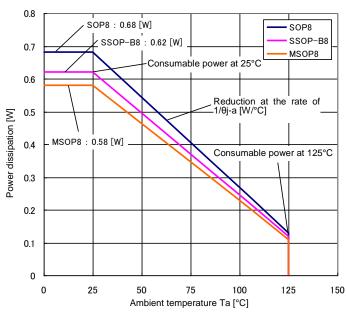

Power dissipation (total dissipation) or PD indicated in the data sheet refers to the power that the IC can consume at the ambient temperature Ta = 25°C (ordinary temperature). The power consumption by the IC causes self-heating, increasing the chip temperature so it is higher than the ambient temperature. The temperature that the chip can tolerate is determined by the maximum junction temperature. Therefore, the consumable power is limited by the thermal reduction curve (derating curve). The power dissipation at 25°C is determined by the temperature that the IC chip inside the package can tolerate (maximum junction temperature) and the thermal resistance (heat radiation property) of the package. In addition, the maximum value of the junction temperature is determined by the manufacturing process.

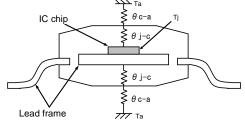

The heat generated by the IC power consumption is radiated through the mold resin or lead frame of the package.

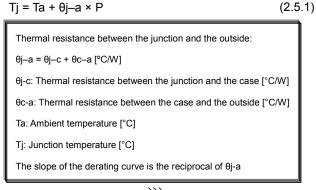

The parameter to describe this heat radiation property (difficulty for the heat to escape) is called thermal resistance and is represented by the symbol  $\theta$ j-a [°C/W].The IC temperature (Junction temperature :Tj) inside the package can be estimated from the thermal resistance. Figure 2.5.1 shows the model for the thermal resistance of the package.  $\theta$ j-a is represented as the sum of the thermal resistance  $\theta$ j-c between the chip and the case (package) and the thermal resistance c-a between the case (package) and the outside. When the thermal resistance  $\theta$ j-a [°C/W], the ambient temperature Ta [°C], and the consumption power P [W] are known, the junction temperature can be calculated with the following equation.

Figure 2.5.1. Thermal resistance of the package

Figure 2.5.2 shows examples of the thermal reduction curve (derating curve). This curve shows how much power the IC can consume at the ambient temperature. It indicates the power that can be consumed without exceeding the temperature that the IC chip can tolerate.

As an example, the chip temperature of the MSOP8 is considered. Since the storage temperature range for this IC is -55 [°C] to 150 [°C], the maximum allowable temperature is 150 [°C]. The thermal resistance of the MSOP8 is  $\theta$ j-a  $\approx$  212.8 [°C/W]. Therefore, the junction temperature when this IC consumes the power of 0.58 [W] at Ta = 25 [°C] is calculated as follows.

Tj = 25 [°C] + 212.8 [°C/W] × 0.58 [W]

$$\approx$$

150 [°C] (2.5.2) The result shows that the junction temperature will reach the maximum allowable temperature of the chip, suggesting the possibility of deterioration or destruction if the power consumption is further increased.

For the thermal reduction curve, the amount of reduction per 1 [°C] is determined by the reciprocal of the thermal resistance. In the figure, the reduction rate is as follows:

5.5 [mW/°C] for the SOP8

5.0 [mW/°C] for the SSOP-B8

4.7 [mW/°C] for the MSOP8

Note: For calculation of the consumption power of op-amps, refer to the next section for the circuit current.

Figure 2.5.2. Examples of the thermal reduction curve (When a 70 mm × 70 mm × 1.6 mm one-layer FR4 glass epoxy substrate is mounted)

### 3 Electrical Characteristics

This technical note explains the electrical characteristics of op-amps and comparators as well as the precautions during actual use.

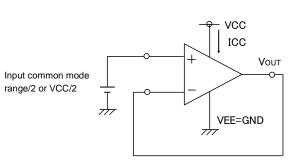

### 3.1 Supply current

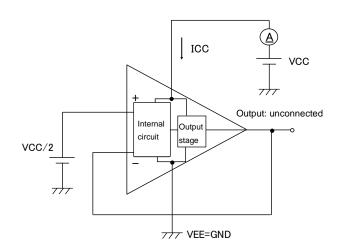

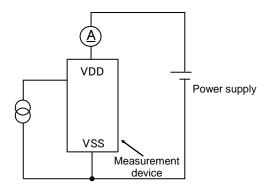

The supply current of an op-amp/comparator represents a current flowing through the IC alone in the no-load and steady state as shown in Figure 3.1.1. Normally, the current flowing from the VCC terminal to the VEE terminal is monitored. The supply current is commonly called a no-signal supply current or quiescent current as well. The input range and the operating voltage range vary with the products, resulting in different conditions. measurement Normally, measurement is performed by applying a voltage in the center of the input common-mode voltage range or in the middle between the supply voltages, VCC and VEE. In addition, the supply current of a comparator takes a different value either under the High or Low condition that is determined by the circuit structure. The value is specified under the condition that gives the higher supply current.

(a) Measurement circuit for the supply current of op-amps

(b) Measurement circuit for the supply current of comparators

Figure 3.1.1. Supply current of op-amp/comparator

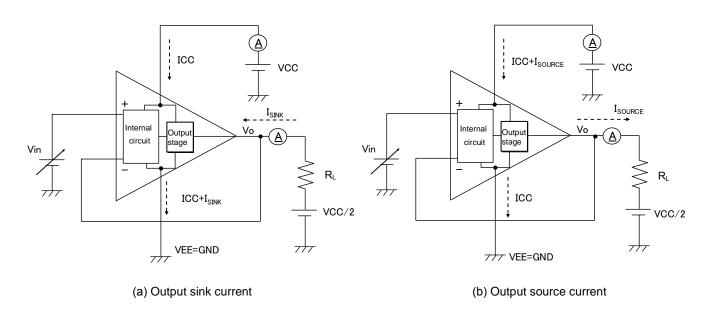

Calculation of the power consumption of op-amps

When calculating the power consumption of an op-amp, it is necessary to consider the output current as well as the supply current.

We explain the calculation of the power consumption step by step. There are two types of power consumption by op-amps: the power consumption caused by the supply current or the output current. First, we show the calculation of the power consumption caused by the supply current. When  $P_{AMP}$  is the power consumed by an op-amp, Equation (3.1.1) becomes the supply current  $\times$  supply voltage based on  $P = current \times voltage$ .

This power consumption is always consumed as long as the supply voltage is applied on the op-amp.

$$P_{AMP} = I_{CC} \times (V_{CC} - V_{EE}) \tag{3.1.1}$$

Figure 3.1.2. Power consumption caused by supply current

Next, we show the calculation of the power consumption caused by the output current.

The power is calculated for the case when an output sink current flows, as shown in Figure 3.1.3 (a).

The output sink current flows when Vo is lower than VCC/2, with which the load resistance ( $R_L$ ) is connected. The power consumption caused by this sink current is described by Equation (3.1.2). The power consumption is determined by the product of the current that flows into the inside of the IC and the difference in potentials between the OUT and VEE terminals.

$$P_{SINK} = I_{SINK} \times (V_O - V_{EE})$$

(3.1.2)

The total power consumption of the op-amp when the sink current exists is represented as Equation (3.1.3).

$$\begin{split} P &= P_{AMP} + P_{SINK} = I_{CC} \times (V_{CC} - V_{EE}) \\ &+ I_{SINK} \times (V_O - V_{EE}) \end{split} \tag{3.1.3}$$

Next, the power is calculated for the case when an output source current flows, as shown in Figure 3.1.3 (b).

The output source current flows when the output voltage (Vo) is higher than VCC/2, with which the load resistance ( $R_L$ ) is connected. The calculation of the power caused by this source current is described by Equation (3.1.4). The power consumption is determined by the product of the current that flows from the inside of the IC and the difference in potentials between the VCC and OUT terminals.

$$P_{SOURCE} = I_{SOURCE} \times (V_{CC} - V_{O}) \tag{3.1.4}$$

The total power consumption of the op-amp when the source current exists is represented as Equation (3.1.5).

$$P = P_{AMP} + P_{SOURCE} = I_{CC} \times (V_{CC} - V_{EE})$$

$$+ I_{SOURCE} \times (V_{CC} - V_O)$$

(3.1.5)

When estimating the power consumption, the larger value of the sink or source current is used.

Figure 3.1.3. Power consumption caused by output current

#### 3.2 Input offset voltage

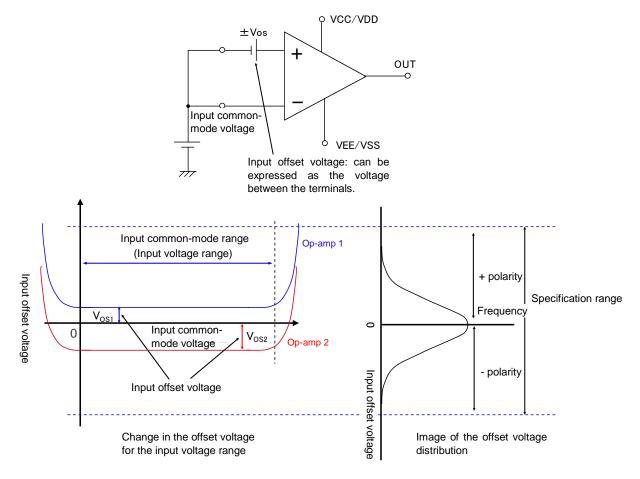

The input offset voltage represents the error voltage of an op-amp or comparator. An ideal op-amp or comparator has the input offset voltage of 0 V. When a common mode (identical) voltage is input to the input terminal of an op-amp or comparator, no output voltage is output in an ideal op-amp. However, when the input offset voltage exists, an output voltage is output in response to the input offset voltage.

The difference in potential between the input terminals that is required to make this output voltage 0 V is referred to as the input offset voltage. This value is the input conversion value. One advantage of expressing the value as the input conversion is as follows: since op-amps and comparators are utilized with various amplification factors and circuit configurations, the influence on the output voltage can be easily estimated by using the input conversion.

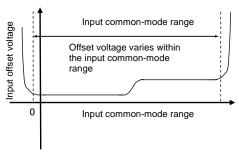

The unit of the input offset voltage is usually [mV] or [ $\mu$ V]. The ideal condition is approached when the value is closer to 0. When the voltage is out of the input common-mode voltage range, the input offset voltage rapidly increases and the circuit cannot be operated as an op-amp or comparator. When the frequency of appearance of the input offset voltage is observed, the observed values follow a normal distribution around 0 V. In other words, the values stochastically distribute within the range specified in the data sheet. While the standard values are described as absolute values, the input offset voltages actually have both + and - polarities. The specific effects of the input offset voltage are explained in the next section.

Figure 3.2.1. Image of input offset voltage

### Effect of input offset voltage

### Op-amp

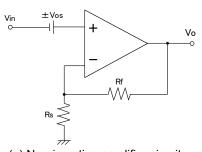

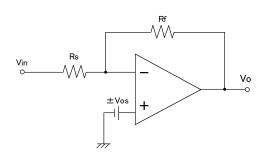

This section explains the effect of the input offset voltage when an amplifier circuit is configured with an op-amp.

For the non-inverting amplifier circuit in Figure 3.2.2 (a), the effect of the input offset voltage is calculated as in Equation (3.2.1).

The input offset voltage is multiplied by the gain and the product is added to the output voltage. When the input offset voltage has the + polarity, the output voltage is higher than the expected value. Conversely, the - polarity results in a lower output voltage than the expected value.

$$V_O = (1 + \frac{R_f}{R_S})V_{in} \pm (1 + \frac{R_f}{R_S})V_{OS}$$

(3.2.1)

Next, the effect of the input offset voltage is determined when the inverting amplifier circuit is configured as in Figure 3.2.2 (b).

$$V_{O} = -\frac{R_{f}}{R_{S}}V_{in} \pm (1 + \frac{R_{f}}{R_{S}})V_{OS}$$

(3.2.2)

As described in Equation (3.2.2), the input offset voltage is multiplied by the amplification factor seen from the + terminal side (i.e., the amplification factor of the non-inverting amplifier circuit) and the product is added to the output of the inverting amplifier circuit. As in the previous case, the output voltage is shifted from the expected value by the product of the input offset voltage multiplied by the gain.

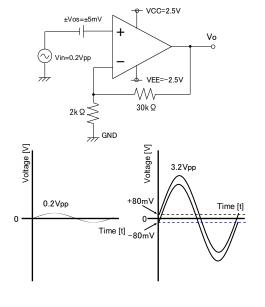

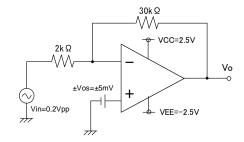

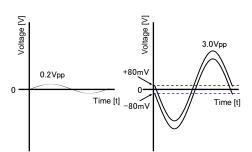

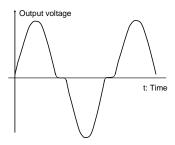

In Figure 3.2.3, the calculation is performed assuming that the input offset voltage is  $\pm 5$  mV. In either circuit, the center of the waveform is shifted by the product of the input offset voltage multiplied by the amplification factor (5 mV × 16). It is necessary to choose an op-amp with an appropriate value for the input offset voltage considering the desired circuit gain.

(a) Non-inverting amplifier circuit

(b) Inverting amplifier circuit

Figure 3.2.2. Amplifier Circuit with Op-Amp

(a) Non-inverting amplifier circuit

(b) Inverting amplifier circuit

Figure 3.2.3. Example of effect of offset voltage

### Comparator

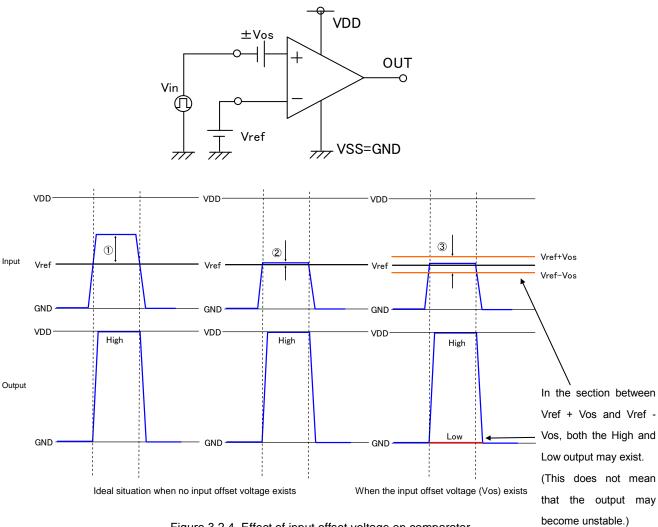

Effect of the input offset voltage on the overdrive voltage. The difference between the voltage to be compared and the reference voltage (Vref) is referred to as the overdrive voltage. When the difference is smaller, the response time tends to be longer. The response time is generally specified at 5 mV, 10 mV, 50 mV, and 100 mV. As an example, consider a comparator with the input offset voltage of 6 mV. In an ideal situation where no input offset voltage exists, the output voltage is switched even when the applied input is only slightly higher or lower than the reference voltage (Vref).

However, when the input offset voltage is 6 mV, the comparator does not respond to the overdrive voltage of 5 mV. In other words, the input offset voltage appears to be added to the reference voltage Vref. When the specification for the input offset voltage is  $\pm Vos$ , the individual circuits may output either High or Low outputs in the section between Vref + Vos and Vref - Vos. Datasheet graphs of response time vs overdrive voltage are measured with compensating for input offset voltage.

Figure 3.2.4. Effect of input offset voltage on comparator

#### Cause of the input offset voltage

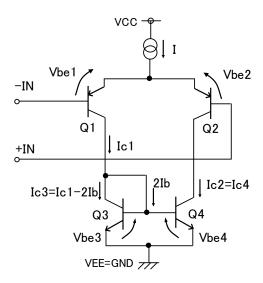

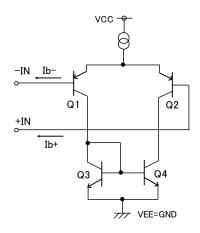

Since the principle of generation is identical for the bipolar and CMOS types, the explanation is given for the bipolar type.

In Figure 3.2.5, the input offset voltage is generated by the difference in the characteristics between transistors Q1 and Q2 as well as between Q3 and Q4. More precisely, variations during the manufacturing process make the voltages between the base and emitter different between Q1 and Q2 as well as between Q3 and Q4. This causes the difference between collector currents Ic3 and Ic4, which flow through Q3 and Q4, respectively. The difference between the collector currents contributes to the generation of the input offset voltage. (The base currents of Q3 and Q4 can also affect the input offset voltage through the variation in the center value. However, this effect is usually minimized by design and can be excluded from the consideration.)

Figure 3.2.5. Differential input stage of op-amp

In addition, the effect of the stress from the package and the board is a cause of input offset voltage generation. This effect generally becomes more significant in the smaller packages. When the stress is received, the piezo-resistance effect is generated by the semiconductor element surface being pushed or the IC chip being bent. The piezoelectric effect caused by this piezo-resistance effect changes the characteristics of transistors.

In op-amps, mainly the differential input stage is subject to the stress effect and the input offset voltage may be changed by the stress from the board after the board is mounted. As a countermeasure, the op-amp should be placed on the center

of the board since the stress is larger in the edges. In addition, since a larger package is less susceptible to the stress, it is effective to choose a package with a larger size when precision is necessary.

#### Temperature drift of the input offset voltage

The input offset voltage varies with temperature. This variation is referred to as the temperature drift. As with the input offset voltage, the temperature drift value is not constant and follows a normal distribution. For some products, the standard values may be described in the data sheet. It should be noted that the input offset voltage may be observed as if drift has been caused by the piezo-resistance effect as mentioned above when the degree of bending of the mounted board changes with the temperature.

# Increase of the input offset voltage caused by the input bias current

When configuring an amplifier circuit with a bipolar op-amp, it is necessary to take a countermeasure against the input bias current. The input offset voltage is increased by the product of the input bias current and the parallel combined resistor value of the resistors that constitute the amplifier circuit.

A countermeasure is to connect the same combined resistance to the other input terminal. This will be explained in more detail in the section for the input bias current.

### 3.3 Input bias current and input offset current

A current flowing from or into the input terminal of op-amps is referred to as the input bias current. In op-amps of the bipolar type, the base current of the transistor connected to the input terminal is the input bias current. When the differential input stage is configured with PNP transistors, the current flows out. Conversely, when the differential input stage is configured with NPN transistors, the current flows in. Many products are designed so that the amount of current falls approximately in the order of nA ( $10^{-9}$  [A]) while some high-speed type products have a bias current in the order of  $\mu$ A ( $10^{-6}$  [A]).

Ideally, op-amps are easier to use when the bias current is smaller. The CMOS type (FET input) op-amps are considered such op-amps. The bias current in the CMOS op-amp is very small and falls in the order of fA (10<sup>-15</sup> [A]) to pA (10<sup>-12</sup> [A]). Therefore, the CMOS op-amps are used as the sensor amplifiers of sensor elements and other elements with high impedance.

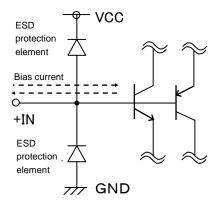

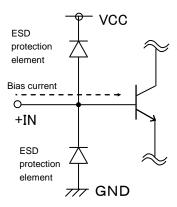

As shown in Figure 3.3.1 (a), the input bias current flows from the input terminal when the op-amp is configured with a PNP transistor as the input transistor.

ESD protection element

Bias current

+IN

ESD protection element

GND

(a) Input ground sense (ground sense single/ dual power supply)

(c) PNP/NPN input (full swing)

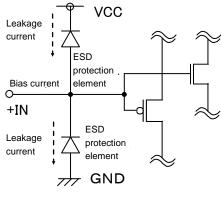

In the case of the NPN input as shown in Figure 3.3.1 (b), the input bias current flows into the terminal. In the full swing op-amp of the bipolar type shown in Figure 3.3.1 (c), the direction of the input bias current changes depending on the operating range. In the range where only the PNP transistor operates, the input bias current flows from the terminal. In the range where both types of transistors operate, the differential current flows, and the polarity becomes the larger one. When only the NPN transistor operates, the input bias current flows into the terminal. Therefore, the polarity of the bias current changes within the input common-mode voltage range.

The input bias current in the CMOS op-amp shown in Figure 3.3.1 (d) is the terminal leakage current. The main cause is the electrostatic protection element connected to the inside of the IC. This current is very small compared with the bipolar type, providing an advantage when connecting op-amps of this type with high-impedance elements such as sensors. In addition, this type of op-amp has a characteristic in which the current tends to increase at a higher temperature since the leakage current increases with temperature.

(b) NPN input (VCC sense)

(d) CMOS input (full swing)

Figure 3.3.1. Input bias current and input transistor

### Effect of input bias current

The difference in the input bias currents in the + and - input terminals is referred to as the input offset current. Since the base current and the leakage current are affected by the performance variation in transistors, the values are not necessarily the same.

The input bias current (lb) and the input offset current (lio) are defined by Equations (3.3.1) and (3.3.2), respectively.

$$Ib = \frac{Ib_{+} + Ib_{-}}{2} \tag{3.3.1}$$

$$Iio = Ib_{+} - Ib_{-}$$

(3.3.2)

(a) Differential input stage

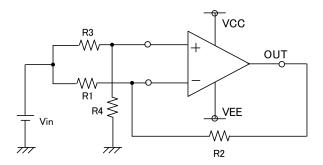

### Cancel of the input bias current

The effect of the input bias current in the inverting amplifier circuit in Figure 3.3.3 is described by Equation (3.3.3).

$$V_{out} = -\frac{R_2}{R_1} V_{in} - (1 + \frac{R_2}{R_1}) \left[ \frac{R_1 R_2}{R_1 + R_2} Ib_{-} - R_3 Ib_{+} \right]$$

(3.3.3)

Arranging Equation (3.3.3) with Equations (3.3.1) and (3.3.2) gives Equation (3.3.4), where Equation (3.3.1) defines the input bias current and Equation (3.3.2) defines the input offset current.

In Equation (3.3.4), the effect of the input bias current can be removed if R3 is set to the same value as the parallel combined impedance of R1 and R2 in order to nullify the lb term. Equation (3.3.4) also shows that the presence of the input offset current affects the output voltage.

$$V_{out} = -\frac{R_2}{R_1} V_{in} - (1 + \frac{R_2}{R_1}) \left[ (\frac{R_1 R_2}{R_1 + R_2} - R_3) I_b - (\frac{R_1 R_2}{R_1 + R_2} + R_3) \frac{I_{io}}{2} \right]$$

(3.3.4)

(b) Input bias current in op-amp

Figure 3.3.2. Input bias current

Figure 3.3.3. Input bias current in inverting amplifier circuit

### 3.4 Input common-mode voltage range

The input common-mode voltage range (V<sub>ICM</sub>) refers to the range of input voltage within which an op-amp operates normally. When a signal outside the input common-mode voltage range is input, the input offset voltage is increased rapidly and the output voltage is saturated, disrupting the normal operation.

The input common-mode voltage range is determined by the circuit configuration of the differential amplifier circuit that is the input circuit of the op-amp.

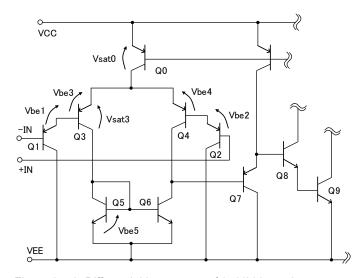

Figures 3.4.1 and 3.4.2 show the differential input stages of the 4558 and 358/2904 series op-amps, respectively. Consider the input common-mode voltage ranges for these two types of op-amp.

The input common-mode voltage range of the 4558 series op-amp is described by Equation (3.4.1), where  $V_{\text{ICM}}$  is the input common-mode voltage. The lower limit of the input common-mode voltage range is the voltage that is required for transistors Q1 and Q2 to operate without being saturated. Conversely, the upper limit of the input common-mode voltage range is the voltage that is required for transistor Q0 to operate without being saturated.

Equation (3.4.2) shows that the 4558 series op-amp has both upper and lower limits between which the transistors can operate. The op-amps of this type are referred to as dual power supply op-amps. Normally, positive and negative power supplies are used with the ground being the middle point potential. However, this type of op-amp can also be used with a single supply if the bias voltage is appropriately adjusted.

Next, the input common-mode voltage range of the 358/2904 series op-amp shown in Figure 3.4.2 is described by Equation (3.4.3). In the 358/2904 series op-amps, level shift circuits Q1 and Q2 are employed so that the input voltage at the ground (VEE) level can be handled. In addition, this type of op-amp is designed so that the collector potentials at Q3 and Q4 can be made nearly equal due to the arrangement of the circuit configuration. This makes Q3 and Q4 saturated at nearly the same voltage.

Equation (3.4.4) shows that the lower limit of the input common-mode voltage is determined by Vsat and Vbe. Since Vsat is generally lower than Vbe, the input common-mode voltage range of the 358/2904 series op-amp can include VEE, allowing the signal input at the ground level.

$$V_{EE} + V_{be6} + V_{be5} + V_{sat2} - V_{be2} < V_{ICMR} < V_{CC} - V_{sat0} - V_{be2}$$

(3.4.1)

If we assume that all Vbe and Vsat values are equal in Equation (3.4.1),

$$V_{EE} + (V_{be} + V_{sat}) < V_{ICMR} < V_{CC} - (V_{sat} + V_{be})$$

(3.4.2)

$$V_{EE} + V_{be5} + V_{Vsat3} - V_{be3} - V_{be1} < V_{ICMR} < V_{CC} - V_{sat0} - V_{be3} - V_{be1}$$

(3.4.3)

If we assume that all Vbe and Vsat values are equal in Equation (3.4.3),

$$V_{EE} + (V_{Vsat} - V_{be}) < V_{ICMR} < V_{CC} - (V_{sat} + 2V_{be})$$

(3.4.4)

Figure 3.4.1. Differential input stage of 4558 series op-amp

Figure 3.4.2. Differential input stage of 358/2904 series op-amp

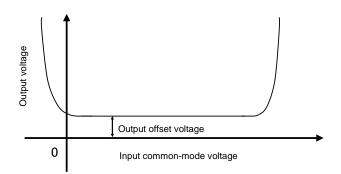

Next, we explain examples of the characteristics and the measurement method of the input common-mode voltage.

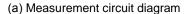

Figure 3.4.3 (a) shows the measurement circuit for the input common-mode voltage. The input voltage is varied with the input terminal of the differential amplifier circuit being used as the common terminal.

Since the common-mode voltage is input, the output voltage should ideally be 0. However, since the input offset voltage actually exists, the output offset voltage is output with the input offset voltage multiplied by the amplification factor as shown in Figure 3.4.3 (b).

Next, we present images of the input common-mode voltage ranges for the 358/2904 and 4558 series op-amps, which we considered in the previous section for the input common-mode voltage range.

As in Figures 3.4.4 and 3.4.5, the input common-mode voltage range limits the input voltage. Therefore, it is necessary to choose an op-amp with an input range adequate for the application to be used. So far, we have explained that the input common-mode voltage range and the input offset voltage are closely related. Regardless of whether the op-amp type is the CMOS (FET input) type or the bipolar type, there are commercially available op-amps of the full swing input type in which the input common-mode voltage range is extended from VEE to VCC. Since such op-amps can secure the input dynamic range even with a low supply voltage, they are ideal for applications operated at a low voltage, such as mobile devices.

(b) Input common-mode voltage vs. output voltage

Figure 3.4.3. Measurement circuit for input common-mode voltage

Figure 3.4.4. Input common-mode voltage range of 4558 series op-amp

Figure 3.4.5. Input common-mode voltage range of 358/2904 series op-amp

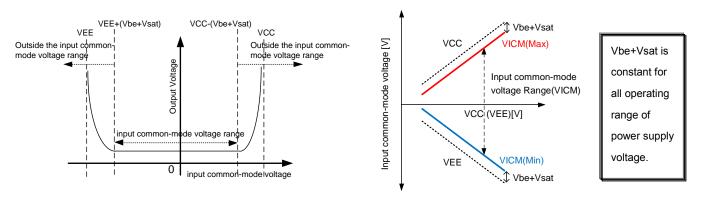

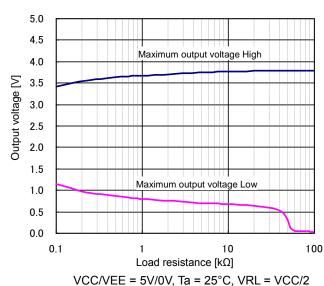

# 3.5 Maximum output voltage (High/Low level output voltage

The maximum output voltage (output voltage range) refers to the voltage range within which an op-amp can output. The voltage values can be separated into the maximum output voltage High (High level output voltage) and the maximum output voltage Low (Low level output voltage).

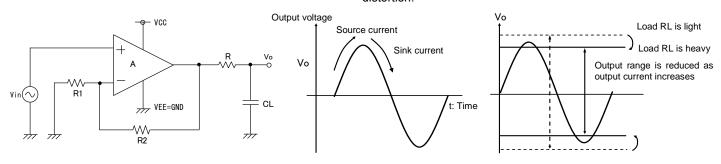

The output voltage range is limited by the output circuit configuration, the supply voltage, and the load condition (the amount of output current).

Next, we explain the output voltage range of the 4558 series low noise op-amp, which is the most standard dual power supply op-amp.

As we mentioned, the output voltage range depends on the output circuit configuration. The limit is imposed because a certain voltage is required for the elements that constitute the circuit, such as transistors, to operate normally.

Figure 3.5.1 shows the output equivalent circuit diagram for the 4558 series op-amp. First, we consider the maximum output voltage High. There are transistors Q1 and Q2 and output protection resistor R1 along the path from the output terminal to the VCC terminal. The voltage necessary for the normal operation is determined by the voltage between the collector and emitter of Q1 (Vce1), the voltage between the base and emitter of Q2 (Vbe2), and when the output source current (Isource) flows, the voltage drop from the Q2 emitter by R1 × Isource. The output voltage range is reduced when the load (RL) is higher (the resistor value is smaller) and a larger source current flows.

vcc Vce1 Q2 Q1 +R1 × Isource R1 Isource Maximum output R2 Isink Vbe3 Q4 be3+Vce4 Q3 +R1 × Isink Vce4 VEE

Figure 3.5.1. Output equivalent circuit diagram for 4558 series op-amp

The maximum output voltage High is described by the following equation.

Maximum output voltage High

$$= VCC - Vce1 - Vbe2 - (R1 \times Isource)$$

(3.5.1)

Next, we consider the maximum output voltage Low. There are transistors Q3 and Q4 and short circuit protection resistor R2 along the path from the output terminal to the VEE terminal. As in the case for the maximum output voltage High, the maximum output voltage Low is determined by the voltage between the collector and emitter of transistor Q4 (Vce4), the voltage between the base and emitter of Q3 (Vbe3), and when the output sink current (Isink) flows, the voltage drop caused by protection resistor R2.

The maximum output voltage Low is described by the following equation.

Maximum output voltage Low

$$= VEE + Vce4 + Vbe3 + (R2 \times Isink)$$

(3.5.2)

Figure 3.5.2 shows an example of the maximum output voltages for the 4558 series op-amp.

As shown in Figure 3.5.2, there exists dead zones on both the positive power supply (VCC) side and the negative power supply (VEE) side where the op-amp cannot operate.

Figure 3.5.2. Example of maximum output voltage for 4558 series op-amp

Next, we consider the output voltage range of the 358/2904 series op-amp, which is the most standard single supply op-amp.

Figure 3.5.3 shows the output equivalent circuit diagram for the 358/2904 series op-amp. As for the maximum output voltage High, there are transistors Q1, Q2, and Q3, and current limit resistor R1 along the path from the output terminal to the VCC terminal. The voltage necessary for this circuit to operate is determined by the voltage between the collector and emitter of Q1 (Vce1), the voltages between the base and emitter of Q2 (Vbe2) and Q3 (Vbe3), and the voltage drop due to the output source current (Isource) by R1 × Isource. The output voltage range is reduced when the load (RL) is higher (the resistor value is smaller) and a larger source current flows.

The maximum output voltage High is described by the following equation.

Maximum output voltage High

Next, we consider the maximum output voltage Low. The 358/2904 series op-amps feature two routes from the output terminal to the VEE terminal. One is the path through transistors Q4 and Q5. The other is the path through Q6. The Q6 path has a structure in which a constant current of 40  $\mu$ A from the output terminal is always supplied by Q6 while the output voltage is Low. This constant current is referred to as the Low level sink current. When the output current is sufficiently smaller than 40  $\mu$ A, the output voltage Low is determined by the voltage between the collector and emitter of Q6 (Vce6).

VCC Vce1 Vbe2+Vbe3+Vce1 Q2 Q1 +R1 × Isource Q3 Vbe2 Isource Maximum Vbe3 output voltage range R1 Vce6 Isink Isink (Isink << 40 u A) RL Vbe4+Vce5 (Isink > 40 μ A) Vce6 VRL 06Vce5 Constant current source: 40 uA

Figure 3.5.3. Output equivalent circuit for 358/2904 series op-amp

Since this Low level output voltage is very small (around 10 mV), the output voltage can be output nearly at the ground level. When the output sink current becomes larger than 40  $\mu$ A, the output sink current begins to flow into Q4. The voltage necessary for Q4 to operate is determined by the voltage between the collector and emitter of Q5 and the voltage between the base and emitter of Q4.

The maximum output voltage Low is described by the following equation.

Maximum output voltage Low

= VEE + Vce6 (Isink <

$$40 \mu A$$

) (3.5.4)

Maximum output voltage Low

= VEE + Vce5 + Vbe4 (Isink > 40

$$\mu$$

A) (3.5.5)

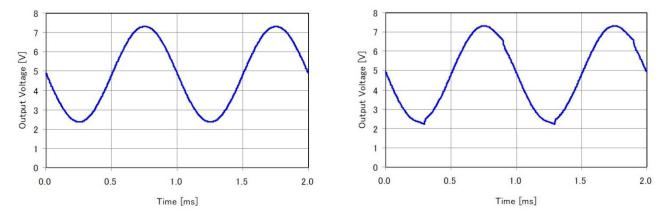

In this way, the different circuits operate in the 358/2904 series op-amps depending on the amount of the output sink current. Therefore, when the 358/2904 series op-amps are used with the load current value being near the Low level sink current of  $40~\mu A$ , the Low level voltage varies as the output circuits are switched, causing a distortion in the waveform.

This distortion is referred to as the crossover distortion. We explain this distortion in detail later.

Figure 3.5.4 shows an example of the maximum output voltages for the 358/2904 series op-amp. As shown in Figure 3.5.4, there exists a dead zone on the positive power supply (VCC) side where the op-amp cannot operate. On the negative power supply (VEE) side, the figure demonstrates that a voltage near VEE (ground) can be output in some conditions.

Figure 3.5.4. Example of maximum output voltage for 358/2904 series op-amp

### 3.6 Large signal voltage gain (open loop gain)

This refers to a gain with respect to the voltage difference between + and - input terminals of op-amps/comparators.

The standard values specified in the data sheet are the voltage gains with respect to a DC current. To minimize the gain error that is generated when a feedback circuit is configured, a high voltage gain (high open loop gain) is generally considered ideal. When the output voltage is Vout and the difference in input potentials is V<sub>IN d</sub>, the voltage gain (Av) is given by the following equation.

$$Av = \frac{V_{OUT}}{V_{IN-d}} \tag{3.6.1}$$

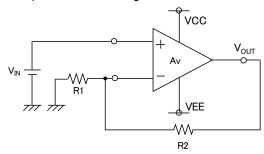

Take a non-inverting amplifier circuit shown in Figure 3.6.1 as an example to consider the gain error.

Figure 3.6.1. Non-inverting amplifier circuit

The output voltage (V<sub>OUT</sub>) is given by the following equation.

$$V_{OUT} = \left(1 + \frac{R_2}{R_1}\right) \times \frac{1}{1 + \left(1 + \frac{R_2}{R_1}\right) \times \frac{1}{A\nu}} \times V_{IN}$$

(3.6.2)

In Equation (3.6.2), if we assume that Av is  $\infty$ , the gain of the circuit is determined by 1 + R2/R1. Therefore, a gain error occurs when the open loop gain (Av) has a finite value.

When R1 = 1 [ $k\Omega$ ], R2 = 10 [ $k\Omega$ ], Av = 80 dB (10,000 times), the amplification factor is 11 in an ideal situation.

$$V_{OUT} = (11) \times \frac{1}{1 + (11) \times \frac{1}{10000}} \times V_{IN} = \frac{11}{1.0011} \cong 10.988$$

(3.6.3)

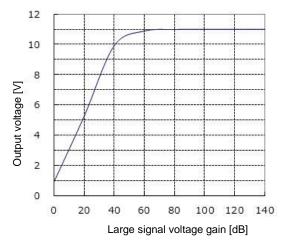

V<sub>OUT</sub> is given by Equation (3.6.3), resulting in an amplification factor less than 11. The difference from the ideal situation is referred to as the gain error. Figure 3.6.2 shows the relation between the output voltage and the amplification factor of a large signal voltage gain.

Figure 3.6.2. Relation between output voltage and large signal voltage gain

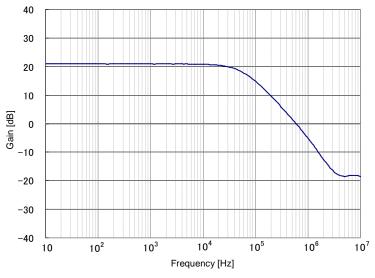

The voltage gain depends on the frequency. It is attenuated as the input signal frequency is increased. Therefore, the gain error increases at a higher frequency. Figure 3.6.3 shows an example of the frequency characteristic of the voltage gain in the circuit shown in Figure 3.6.1 (using a BA2904 op-amp).

Figure 3.6.3. Frequency characteristic of the voltage gain

### 3.7 CMRR (Common Mode Rejection Ratio)

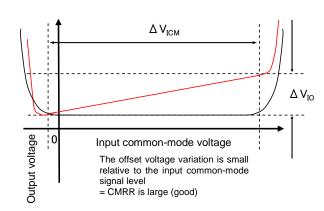

The common mode rejection ratio (CMRR<sub>AMP</sub>) is the ratio of variation in the output voltage when the input common-mode voltage is varied, expressed in dB. Generally, the CMRR specified in the data sheet represents the ratio of the DC input common-mode voltage and the variation in the input offset voltage ( $\Delta V_{IO}$ ) when the DC input common-mode voltage is varied. This ratio expresses the value of the CMRR for the op-amp itself. We will explain the details in the next section.

$$CMRR_{AMP} = 20\log\left(\frac{\Delta V_{ICM}}{\Delta V_{IO}}\right)$$

(3.7.1)

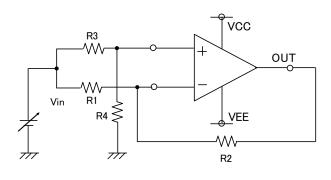

Next, we explain a view about the common mode rejection ratio when an amplifier circuit is configured.

When an amplifier circuit is configured with external resistors, an error in resistance (pair mismatch) causes an offset voltage in the amplifier circuit. This offset voltage due to the resistance error affects the common mode rejection ratio in the same way that the input offset voltage of op-amps does. The CMRR<sub>RES</sub> due to the resistance error in the amplifier circuit can be calculated with the following equation. Here, we suppose that the CMRR of the op-amp is ideal (CMRR<sub>AMP</sub> =  $\infty$ ). The error mentioned here is a mismatch between R1 and R3 as well as between R2 and R4.

G is the gain (R2/R1) of the amplifier circuit. Suppose that  $CMRR_{RES} = G_{DIFF}/G_{CM}$ , where  $G_{DIFF}$  is the amplification factor for the differential voltage and  $G_{CM}$  is the amplification factor for the common-mode voltage (the derivation is omitted).

$$CMRR_{RES} = \frac{1+G}{1-\frac{R_2R_3}{R_1R_4}}$$

(3.7.2)

In Figure 3.7.1 (a), the CMRR of the whole circuit (CMRR<sub>ALL</sub>) is described by Equation (3.7.3).

$$CMRR_{ALL} = \frac{1+G}{\frac{1+G}{CMRR_{AMP}} + \left(1 - \frac{R_2 R_3}{R_1 R_4}\right)}$$

(3.7.3)

Therefore, a resistance mismatch affects the common mode rejection ratio of an associated amplifier circuit. It can be seen that CMRR<sub>ALL</sub> is limited even when an op-amp with a large CMRR (CMRR<sub>AMP</sub>) is used.

In the next section, we further consider the meaning of the common mode rejection ratio of op-amps.

(a) Measurement circuit diagram

(b) Variation in the input offset voltage

Figure 3.7.1. Relation between input offset voltage and CMRR

Common mode rejection ratio of op-amps

Introductory books on circuit design define the CMRR of an op-amp itself as CMRR = Ad/Ac expressed in dB, where Ad (the differential voltage gain) is the gain with respect to the difference in input voltages of the op-amp and Ac (the common-mode voltage gain) is the gain with respect to the input common-mode voltage. This definition corresponds to Equation (3.7.1).

Ideally, an op-amp should amplify the difference in voltages between its + and - input terminals by the gain of the amplifier. However, the differential voltage gain and the common-mode voltage gain are altered in an actual op-amp due to changes in the DC operating points (current and voltage) inside the circuit that are caused by a variation in the input common-mode voltage. As a result, the input offset voltage is varied and a variation in the output voltage is observed.

When the gain with respect to the difference in the input voltages is Ad (the differential voltage gain), the gain with respect to the input common-mode voltage is Ac (common-mode voltage gain), the potential of the + input terminal is Vin\_p, and the potential of the - input terminal is Vin\_n, the output voltage of the op-amp can be described by the following equations.

$$V_{OUT} = Ad \times (V_{in-p} - V_{in-n}) + Ac \times V_{ICM}$$

(3.7.4)

$$V_{OUT} = Ad \times \left( (V_{in_{-}p} - V_{in_{-}n}) + \frac{Ac}{Ad} \times V_{ICM} \right)$$

(3.7.5)

V<sub>ICM</sub> is the input common-mode voltage and equal to (Vin\_p + Vin\_n)/2.

In Equation (3.7.5), the term, (Ac/Ad)  $\times$  V<sub>IC</sub>, represents an error term due to the input common-mode voltage and can be considered the input offset voltage.

$$V_{IO} = \frac{Ac}{Ad} \times V_{ICM} \tag{3.7.6}$$

From Equation (3.7.6), a variation in the input offset voltage due to a variation in the input common-mode voltage is provided as follows.

$$\frac{\Delta V_{ICM}}{\Delta V_{IO}} = \frac{Ad}{Ac} = CMRR \tag{3.7.7}$$

Equation (3.7.7) shows that the ratio of the variations is equivalent to the ratio of the input common-mode voltage and

the input offset voltage as mentioned above.

As an example, we use Equation (3.7.7) to calculate the effect of a variation in the input common-mode voltage on the output.

We calculate  $V_{IO\_10}$  when  $V_{IO\_0} = 1$  [mV] and CMRR = 80 [dB] = 10,000 [times], where  $V_{IO\_10}$  is the input offset voltage when  $V_{IC} = 10$  [V],  $V_{IO\_0}$  is the offset voltage when  $V_{IC} = 0$  [V], and  $V_{IC}$  is the input common-mode voltage.

$$CMRR = \frac{V_{IC\_10} - V_{IC\_0}}{V_{IO\_10} - V_{IO\_0}}$$

(3.7.8)

$$V_{IO_{-10}} = \frac{10[V]}{CMRR[\text{times}]} + 1[mV] = 2[mV]$$

(3.7.9)

Therefore, when CMRR = 80 [dB], a variation of 10 [V] in the input common-mode voltage increases the input offset voltage by 1 [mV].

The next section explains the mechanism by which the input offset voltage is varied due to a variation in the input common-mode voltage.

Mechanism of the variation in the input offset voltage due to the input common-mode voltage (reference)

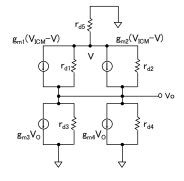

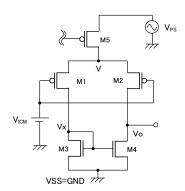

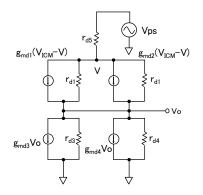

Figure 3.7.2 shows the equivalent circuit for a differential input stage. We explain the mechanism by which the input offset voltage is increased by a variation in the input common-mode voltage. First, we assume characteristics are identical between transistors M1 and M2 as well as between M3 and M4. This means that no input offset voltage is generated by the differential input stage or the active loads. Since the characteristics are identical, the voltages between the gate and source are equal and the currents flowing through differential input transistors M1 and M2 are equal. Next, since the characteristics of active loads M3 and M4 are identical, the currents flowing through the loads are equal. The identical currents and characteristics result in identical drain voltages between active loads M3 and M4. Therefore, we can consider that Vx and Vo is virtually short-circuited in small signal equivalent circuit 1 in Figure 3.7.2 (b). Based on this point, the small signal equivalent circuit is described as small signal equivalent circuit 2 in Figure 3.7.2 (c). Since we can consider that the transistor elements are connected in parallel to each other, it is possible to combine the circuits for simplification. The common-mode voltage gain is calculated with this circuit.

For the calculation of common-mode voltage gain,  $g_m$  is the transconductance of transistors,  $r_d$  is the drain impedance,  $g_d$  is the drain conductance,  $V_{ICM}$  is the input common-mode voltage, and V is the drain voltage of M5.

In addition,  $1/r_d = g_d$ . Form an equation for nodes  $V_O$  and V. Arranging Equation (3.7.10) and using an approximation that  $g_{m4}$ ,  $g_{m2} >> g_{d4}$ ,  $g_{d2}$ , Equation (3.7.11) is obtained (the derivation is omitted).

Equation (3.7.11) shows that the common-mode voltage gain (Ac) is determined by the impedance of transistor M5 and  $g_m$  of the active load. Next, the differential voltage gain can be described by Equation (3.7.12) (the derivation is omitted).

When the input offset voltage is  $V_{IO}$ , CMRR is calculated from Equations (3.7.11) and (3.7.12), resulting in Equation (3.7.13).

Thus, to obtain a smaller common-mode voltage gain ( $A_C$ ),  $r_{d5}$  or  $g_{m4}$  needs to be larger. A larger  $r_{d5}$  means that the current flowing through transistor M5 is less likely to be affected by the input common-mode voltage. However, actual values of  $r_{d5}$  and  $g_{m4}$  are finite and CMRR is therefore limited. In other words, since CMRR is finite, the input offset voltage is varied due to the variation in the input common-mode voltage.

$$g_{d5}V + 2g_{m2}(V_{ICM} - V) + 2g_{d2}(V - V_O) = 0$$

$$2g_{m4}V_O + 2g_{d4}V_O + 2g_{m2}(V_{ICM} - V) + 2g_{d1}(V - V_O) = 0$$

(3.7.10)

$$A_c = \frac{V_O}{V_{ICM}} = \frac{1}{2g_{m4}r_{d5}}$$

(3.7.11)

$$A_d = \frac{V_O}{V_{ind}} = g_{m1}(r_{d2} // r_{d4})$$

(3.7.12)

$$CMRR = \frac{A_d}{A_c} = \frac{V_{ICM}}{V_{ind}} = \frac{V_{ICM}}{V_{IO}} = 2g_{m4}g_{m1}r_{d5}(r_{d2} // r_{d4})$$

(3.7.13)

(a) Equivalent circuit for differential input circuit

(b) Small signal equivalent circuit 1

(c) Small signal equivalent circuit 2

Figure 3.7.2. Equivalent circuit diagram for op-amp differential input stage

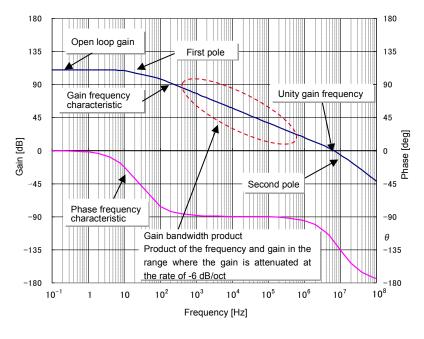

Next, we explain the frequency characteristic of the CMRR. The differential voltage gain shown in Equation (3.7.13) is the gain with respect to a given DC voltage. This gain actually has a frequency characteristic. As shown in Equation (3.7.13), the differential voltage gain of op-amps is closely related to the CMRR. The differential voltage gain of the op-amp is reduced at the rate of -6 dB/oct (= -20 dB/dec) as the frequency increases, due to the first pole of the differential input stage.

This causes a simultaneous reduction in the CMRR. Figure 3.7.3 shows the frequency characteristic of the CMRR. It is important to consider the frequency characteristic of the CMRR when actually using op-amps.

Figure 3.7.3. CMRR frequency characteristic

Rev.F

### 3.8 PSRR (Power Supply Rejection Ratio)

The power supply rejection ratio (PSRR) is the amount of variation in the input offset voltage when the power supply voltage is varied, expressed as a ratio. Generally, the standard values described in the data sheet are the ratio of variation in the input offset voltage when a DC voltage supply

$$PSRR = 20\log\left(\frac{\Delta VCC}{\Delta V_{lo}}\right) \tag{3.8.1}$$

PSRR is generally defined by PSRR = Ad/Ap, where Ad is the gain with respect to the difference in the input voltages of the amplifier (differential voltage gain) and Ap is the gain with respect to the power supply voltage. This definition has the same meaning as Equation (3.8.1).

Ideally, an op-amp should increase the difference in voltages between its + and - input terminals by the gain of the amplifier. However, the differential voltage gain and the power supply variation gain are altered in an actual op-amp due to changes in the DC operating points (current and voltage) inside the circuit that are caused by changing the power supply voltage. As a result, the input offset voltage varies and a variation in the output voltage is observed.

When the gain with respect to the difference in the input voltages is Ad (the differential voltage gain), the gain with respect to the power supply voltage is Ap (power supply voltage gain), the potential of the + input terminal is Vin\_p, and the potential of the - input terminal is Vin n, the output voltage of the op-amp can be expressed by the following equations.

$$V_{OUT} = Ad \times (V_{in_{-}p} - V_{in_{-}n}) + Ap \times VCC$$

(3.8.2)

$$V_{OUT} = Ad \times \left( (V_{in_{-}p} - V_{in_{-}n}) + \frac{Ap}{Ad} \times VCC \right)$$

(3.8.3)

In Equation (3.8.3), the term, (Ap/Ad) × Vcc, represents an error term due to the power supply voltage and can be considered the input offset voltage.

$$V_{IO} = \frac{Ap}{Ad} \times VCC \tag{3.8.4}$$

From this relational expression, the variation in the input offset voltage with respect to the variation in the power supply voltage is described by Equation (3.8.5). Therefore, PSRR is

equivalent to the ratio of the variation in the input offset voltage with respect to the power supply voltage variation mentioned above.

$$\frac{\Delta VCC}{\Delta V_{IO}} = \frac{Ad}{Ap} = PSRR \tag{3.8.5}$$

As an example, we use Equation (3.8.5) to calculate Vio 20 when Vio\_10 = 1 [mV], where Vio\_20 and Vio\_10 are the input offset voltages when Vcc = 20 [V] and 10 [V], respectively. Suppose that PSRR = 80 [dB] (= 10,000 times).

$$PSRR = \frac{V_{CC_{20}} - V_{CC_{10}}}{V_{IO_{20}} - V_{IO_{10}}} = 10000 \text{[times]}$$

(3.8.6)

$$V_{lO_{-10}} = \frac{10[V]}{10000[\text{times}]} + 1[mV] = 2[mV]$$

(3.8.7)

Therefore, when PSRR = 80 [dB], a variation of 10 [V] in the power supply voltage increases the input offset voltage by 1 [mV].

When an amplifier circuit is configured, the error voltage that is multiplied by the gain of the amplifier circuit is output as an error in the output voltage.

When a non-inverting amplifier circuit with a gain of 100 [times] is configured, a variation of 10 [V] in the power supply voltage causes a variation of 100 [mV] in the output voltage.

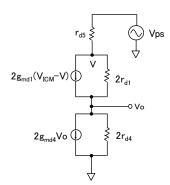

Since we can consider that the transistor elements are

connected in parallel to each other, it is possible to combine

the circuits for simplification. The power supply voltage gain is

calculated with this circuit. For the calculation of power supply

voltage gain, gm is the transconductance of transistors, rd is

the drain impedance,  $g_d$  is the drain conductance,  $V_{\text{ICM}}$  is the

input common-mode voltage, and V is the drain voltage of M5.

In addition,  $1/r_d = g_d$ . Form Equation (3.8.8) for nodes  $V_O$  and

Arranging Equation (3.8.8) and using approximations that

V-Vps=Vds and  $g_{m4}$ ,  $g_{m2} >> g_{d4}$ ,  $g_{d2}$ , Equation (3.8.9) is

Equation (3.8.9) shows that the power supply voltage gain

(A<sub>P</sub>) is determined by the impedance of transistor M5 and g<sub>m</sub>

of the active load. Next, the differential voltage gain can be

When the input offset voltage is V<sub>IO</sub>, PSRR is calculated from

Equations (3.8.9) and (3.8.10), resulting in Equation (3.8.11).

Thus, to obtain a smaller power supply voltage gain (Ap), rd5

or  $g_{m4}$  needs to be larger. A larger  $r_{d5}$  means that the current flowing through transistor M5 is less likely to be affected by

the input common-mode voltage. However, actual values of

$r_{d5}$  and  $g_{m4}$  are finite and PSRR is therefore limited. In other

words, since the PSRR is finite, the input offset voltage is

varied due to the variation in the input common-mode voltage.

described by Equation (3.8.10). (The derivation is omitted.)

obtained (the process is omitted).

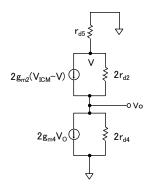

Mechanism of the variation in the input offset voltage due to the power supply voltage (reference)

Figure 3.8.1 shows the equivalent circuit for a differential input stage. Now we will explain the mechanism by which the input offset voltage is increased by a variation in the power supply voltage. First, we assume that the characteristics are identical between transistors M1 and M2 as well as between M3 and M4. This means that no input offset voltage is generated by the differential input stage or the active loads. Since the characteristics are identical, the voltages between the gate and source are equal and the currents flowing through differential input transistors M1 and M2 are equal. However, when considering the power supply voltage variation, the variation in the power supply also alters the input common-mode voltage range. Therefore, the input voltage level should always be adjusted to a value in the middle of the input common-mode voltage range.

Next, since the characteristics of active loads M3 and M4 are identical, the currents flowing through the loads are equal. The identical currents and characteristics result in identical drain voltages between active loads M3 and M4. Therefore, we can consider that Vx and Vo is virtually short-circuited in small signal equivalent circuit 1 in Figure 3.8.1 (b). Based on this point, the small signal equivalent circuit is described as small signal equivalent circuit 2 in Figure 3.8.1 (c).

$$g_{d5}(V - V_{ps}) + 2g_{m1}(V_{ICM} - V) + 2g_{d1}(V - V_{O}) = 0$$

$$2g_{m4}V_{O} + 2g_{d4}V_{O} + 2g_{m1}(V_{ICM} - V) + 2g_{d1}(V - V_{O}) = 0$$

(3.8.8)

$$A_P = \frac{V_O}{V_{ds}} = \frac{g_{e5}}{2g_{m4}} = \frac{1}{2g_{m4}r_5}$$

(3.8.9)

$$A_d = \frac{V_O}{V_{ind}} = g_{m1}(r_{d2} // r_{d4})$$

(3.8.10)

$$PSRR = \frac{A_d}{A_P} = \frac{V_{ds}}{V_{ind}} = \frac{V_{ds}}{V_{IO}} 2g_{m4}r_5g_{m1}(r_{d2} // r_{d4})$$

(3.8.11)

(a) Equivalent circuit for differential input circuit

(b) Small signal equivalent circuit 1

(c) Small signal equivalent circuit 2

Figure 3.8.1. Equivalent circuit diagram for op-amp differential input stage

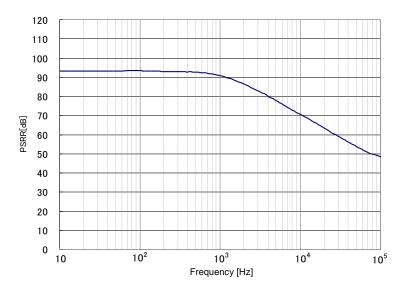

As with the CMRR, the value of the PSRR is reduced as the input signal frequency increases. As shown in Equation (3.8.11), the differential voltage gain of op-amps is closely related to the PSRR. The differential voltage gain of the op-amp is reduced at the rate of -6 dB/oct (= -20 dB/dec) as the frequency increases, due to the first pole of the differential input stage. This causes a simultaneous reduction in the PSRR.

Therefore, any ripple noise with a high frequency on the power supply line will alter the output voltage significantly, causing output noise. As a countermeasure against power supply noise, you can connect a bypass capacitor near the power supply terminal of op-amps. Figure 3.8.2 shows an example of the frequency characteristic of the power supply rejection ratio.

Figure 3.8.2. PSRR frequency characteristic

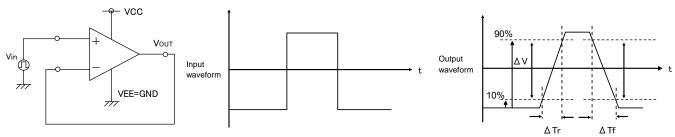

#### 3.9 SR (Slew Rate)

The slew rate is a parameter that represents the operating speed of op-amps. This parameter describes the rate of variation that the output voltage can undertake per specified unit time. For example, 1 [V/µs] means that the voltage can be varied by 1 [V] in 1 [µs].

An ideal op-amp can exactly follow any input signal and output the output signal. However, the slew rate sets limits on the output in practice. The slew rate describes how much the output voltage can change per unit time when a rectangular wave pulse with a steep rise and fall is input. Equation (3.9.1) shows the definition of slew rate.

The slew rates for the rise and fall are calculated with Equation (3.9.1).

$$SR_r = \frac{\Delta V}{\Delta Tr}$$

$SR_f = \frac{\Delta V}{\Delta T_f}$  (3.9.1)

The slew rate specified in the data sheet is based on the rate for either "rise" or "fall", whichever is the slower. The slew rate represents the maximum slope of the op-amp output signal. When the signal has a steeper change, the output waveform cannot follow the signal and will be distorted. Since the slew rate is the rate of output change, it is not affected when an amplifier circuit is configured.

Consider the meaning of the slew rate when an op-amp is actually used. Op-amps are used for the amplification of both DC and AC signals. As mentioned above, since op-amps have a limit on their response speed, there are signals that op-amps cannot handle. We explain a voltage follower configuration shown in Figure 3.9.1. For a given DC voltage input, limits are set by the input and output voltage ranges. For an AC signal with a frequency, additional limits are set by the gain bandwidth product and the slew rate. Here, we consider the relation between the amplitude and frequency, namely the slew rate.

We calculate the maximum frequency that an op-amp can output. To determine the maximum frequency, we calculate the slew rate that is required to output a waveform as shown in Figure 3.9.2.

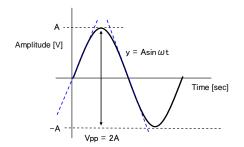

Figure 3.9.2 Waveform of a sine wave

$$y = A \sin \omega t \tag{3.9.2}$$

Since the slew rate is the slope of the tangent to the sine wave, we differentiate Equation (3.9.2).

$$\frac{dy}{dt} = A\omega\cos\omega t \qquad \omega t = 0 \tag{3.9.3}$$

From Equation (3.9.3), the slew rate is described by

$$SR = A\omega \quad \omega = 2\pi f$$

(3.9.4)

In addition, since the amplitude of the sine wave is given by Vpp = 2A (peak-to-peak), Equation (3.9.4) can be rearranged as follows.

$$f = \frac{SR}{2\pi \times A} = \frac{SR}{\pi V_{pp}} [Hz] \qquad V_{pp} = \frac{SR}{\pi f} [V]$$

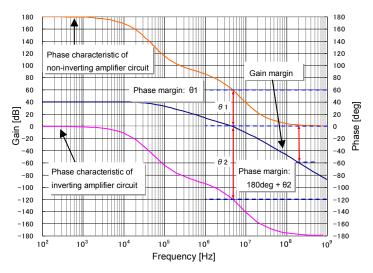

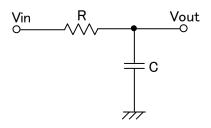

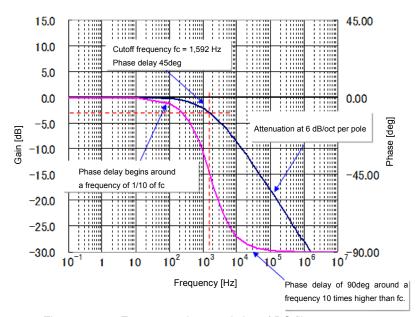

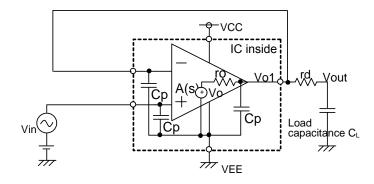

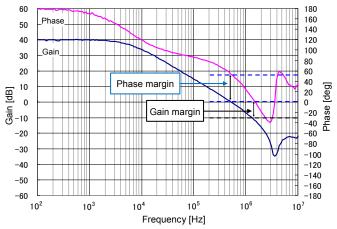

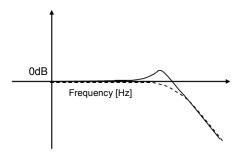

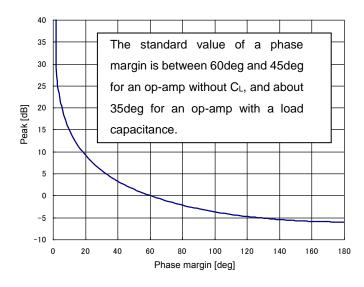

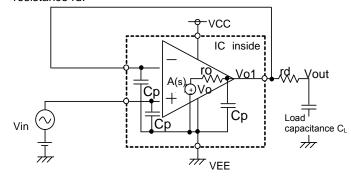

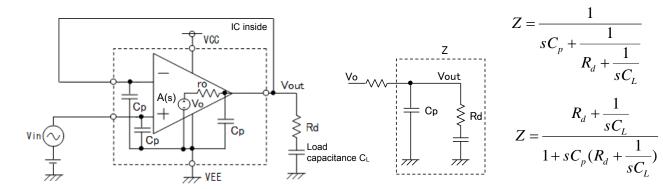

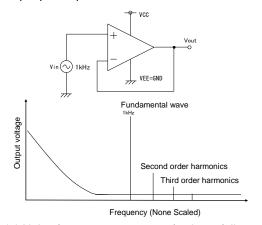

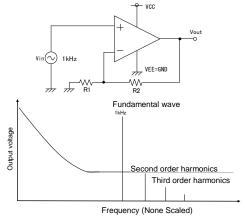

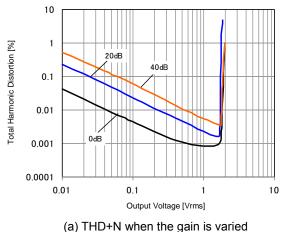

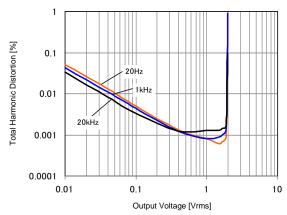

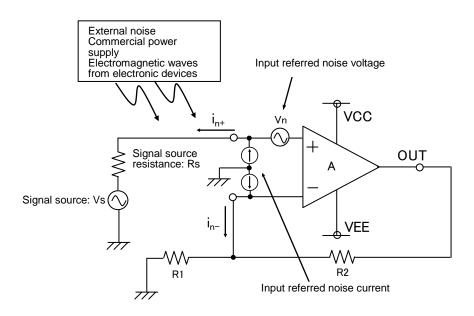

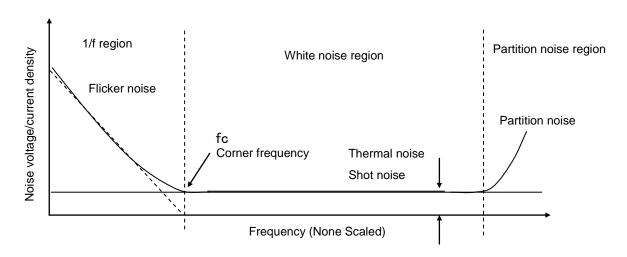

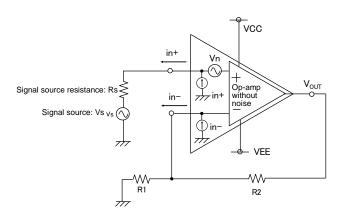

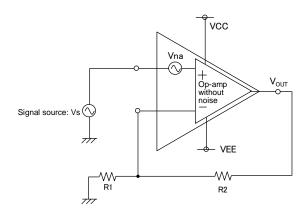

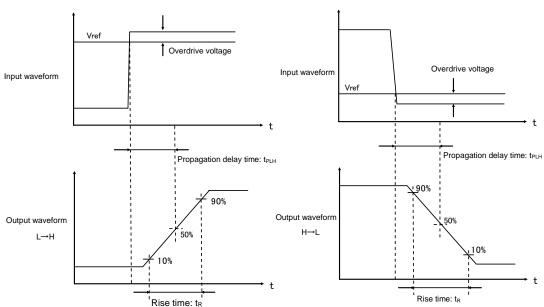

(3.9.5)