# SVM7560 Series

### **Melody IC**

- Winder choices of working voltage

- Low power consumption and low voltage

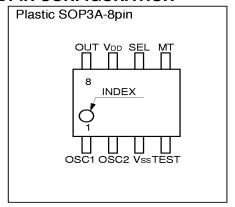

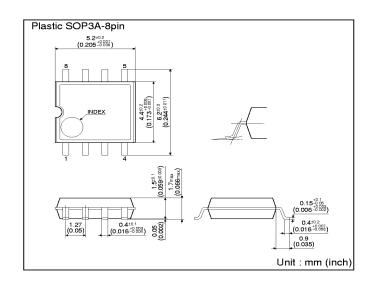

- SOP3A-8pin small-sized package

#### **■ DESCRIPTION**

SVM7560 Series devices are CMOS LSIs which can play music melodies and generate chime or alarm sound according to musical information previously programmed into a mask ROM integrated into them. The capacity of the ROM being used for storage of such music information is of 128 words and upto two numbers

of music melodies under two different sound sources can be optioned for storage into it.

Also, the total integration (for mask option) of the CR oscillation circuit and integration of the envelope adding circuit for attenuation of performed music sound eliminate the need of external parts. Moreover, employing a small-sized package, they are most suitable for space-saving applications but requiring comfortable sound quality such as of holding time melody source of telephones.

#### **■ FEATURES**

| Attenuation of sound      Loudspeaker drive     | <ul> <li>128 words (optional word allocation for each melody)</li> <li>24 words (optional word allocation for each melody)</li> <li>Dual sound sources</li> <li>32.768KHz, 47.520KHz(mask option selection)</li> <li>1) Changing the melody midway during performance:     Possible or Not possible (mask option selection)</li> <li>2) Selection of the reference sound frequency:     When selecting the signal source frequency of     32.768KHz: A4 = 440Hz (standard) or C4 = 256Hz     When selecting the signal source frequency of     47.520KHz: A4 = 440Hz</li> <li>3) Choices of the reference signal source: External clock     input or integrated CR oscillation (using both of the     integrated C and R) or integrated CR oscillation (using     the integrated C only but the R is for external installation)</li> <li>4) Performance method choice: Level hold or one-shot C     Integrated envelope adding circuit</li> </ul> |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| should be used)  Low voltage operation  Package |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                                               | 1 11 /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **SEIKO EPSON CORPORATION**

### **EPSON**

#### **■ BLOCK DIAGRAM**

#### **■ PIN CONFIGURATION**

#### **■ PIN DESCRIPTION**

| Pin No. | Pin name | I/O  | Integrated pull down | Function                                                                                                                                  |  |  |

|---------|----------|------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1       | OSC1     | I/NC | Not equipped         | (1) When the external clock input mode is selected by mask option:                                                                        |  |  |

| 2       | OSC2     | 0    | 1                    | Enter square waves of 32.768KHz or 47.520KHz to the OSC1 pin as the reference signal source.                                              |  |  |

|         |          |      |                      | (2) When the integrated CR oscillation is selected by mask option:                                                                        |  |  |

|         |          |      |                      | When using an external "R", insert a resistor between the OSC1 and OSC2 to adjust the oscillation                                         |  |  |

|         |          |      |                      | frequency by the resistance of the resistor.                                                                                              |  |  |

|         |          |      |                      | When using integrated CR, keep the OSC1 and OSC2 open.                                                                                    |  |  |

| 3       | Vss      | -    | _                    | Negative supply pin or grounding pin                                                                                                      |  |  |

| 4       | TEST     | I    | Equipped             | This is the IC test input pin.                                                                                                            |  |  |

| 5       | MT       | J    | Equipped             | When "High" level is input, the device goes into working mode to control starting and stopping of the                                     |  |  |

|         |          |      |                      | performance in accordance with the performance method being designated by the option.                                                     |  |  |

| 6       | SEL      | I    | Equipped             | Melody 1 and melody 2 can be selected in the binary code order by entering "0" or "1" into this pin.                                      |  |  |

|         |          |      |                      | (1) When "changing the melody midway during performance - not possible" is selected by mask op-                                           |  |  |

|         |          |      |                      | tion:                                                                                                                                     |  |  |

|         |          |      |                      | After going into the working mode on input of "High" to the MT pin, the input level of either "Low" or                                    |  |  |

|         |          |      |                      | "High" which was applied to the SEL pin just before starting performance is adopted and the per-                                          |  |  |

|         |          |      |                      | forming melody shall not thereafter change even if the input level to the SEL pin changes.                                                |  |  |

|         |          |      |                      | (2) When "changing the melody midway during performance - possible" is selected by mask option:                                           |  |  |

|         |          |      |                      | Each time the level of the input to the SEL pin changes during a working mode, the melody                                                 |  |  |

|         |          |      |                      | changes and, when changing the melody, performance shall be resumed from the beginning of the melody.                                     |  |  |

| 7       | Vpp      |      |                      | This pin outputs square wave signals.                                                                                                     |  |  |

|         |          |      |                      |                                                                                                                                           |  |  |

| 8       | OUT      | 0    | _                    | With the audio signals, the key melody and accompaniment, respectively, are attenuated under a cell                                       |  |  |

|         |          |      |                      | tain time constant and respective audio outputs of the key melody and accompaniment are mixed by the                                      |  |  |

|         |          |      |                      | mixing resistor before being output.                                                                                                      |  |  |

|         |          |      |                      | This pin should therefore be connected to the input pin of a pre-amp via a variable resistor for volume control, coupling-capacitor, etc. |  |  |

|         |          |      |                      | control, coupling-capacitor, etc.                                                                                                         |  |  |

#### ■ ABSOLUTE MAXIMUM RATINGS

(Vss=0V)

| Rating                    | Symbol      | Ratings          | Unit |

|---------------------------|-------------|------------------|------|

| Supply voltage            | <b>V</b> DD | -0.3 to +7.0     | ٧    |

| Terminal voltage          | Vıo         | -0.2 to VDD +0.2 | V    |

| Working temperature range | Topr        | -20 to +85       | °C   |

| Storage temperature range | Tstg        | -65 to +150      | °C   |

#### **■ ELECTRICAL CHARACTERISTICS**

(VDD=0.9 to 5.5V, Vss=0V, Ta=25°C)

| Characteristic                        | Symbol                                | Applicable Pin | Condition                                                                                                       |                               | Min.        | Тур.         | Max.        | Unit     |

|---------------------------------------|---------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------|-------------|--------------|-------------|----------|

| Working voltage                       | VDD                                   | VDD            | OSC1=32.768 or 47.520KHz Whene xternal clock input mode is selected. Note 1.                                    |                               | 0.9         | 3.0          | 5.5         | ٧        |

| High level input                      | VIN                                   | MT, SEL        | _                                                                                                               |                               | VDD         | -            | VDD         | ٧        |

| voltage                               |                                       | OSC1           | External clock signal input                                                                                     | t                             | -0.3        |              |             |          |

| Low level input                       | Vı∟                                   | MT, SEL        | _                                                                                                               |                               | 0           | _            | 0.3         | V        |

| voltage                               |                                       | OSC1           | External clock signal input                                                                                     | t                             |             |              |             |          |

| High level input                      | liH1                                  | SEL            | VIH1=VDD, Standby mode                                                                                          |                               | _           | _            | 0.3         | μА       |

| current (1)                           |                                       | OSC1           | VIH1=VDD, External clock s                                                                                      | signal input                  |             |              |             |          |

| High level input IIH2 SEL current (2) |                                       | SEL            | Working mode VIH2=VDD                                                                                           | V <sub>DD=1</sub> .5V<br>3.0V | 0.4<br>3.0  | 1.8<br>10.0  | 4.0<br>30.0 | μΑ<br>μΑ |

|                                       |                                       | MT             | Vih2=VDD                                                                                                        | 5.0V                          | 12.5        | 32.0         | 80.0        | μА       |

| Low level input                       | lıL                                   | MT, SEL        | V <sub>IL</sub> =0V                                                                                             |                               | -0.3        | -            | -           | μA       |

| current                               |                                       | OSC1           | VIL=0V, External clock signal input                                                                             |                               |             |              |             |          |

| Output impedance                      | Zout                                  | OUT            | When attacking both of the<br>and accompaniment at the<br>and when determining the<br>respective DAC levels for |                               | 150         | 300          | KW          |          |

| Standby mode current consumption      | IDDS                                  | VDD            | All input terminals = 0V OUT = No load standby mode                                                             | -                             | 0.1         | 1.0          | μА          |          |

| Working mode average current          |                                       |                | VDD = 1.5V                                                                                                      | _                             | 20 (Note 2) | 80 (Note 2)  | μА          |          |

| consumption                           |                                       |                | When CR oscillation<br>is selected:<br>fck = 32.768KHz<br>or 47.520KHz                                          | VDD = 3.0V                    | -           | 40 (Note 2)  | 100(Note 2) | μΑ       |

|                                       | OUT = No load Vpb = 5.0V standby mode |                | VDD = 5.0V                                                                                                      | _                             | 90 (Note 2) | 200 (Note 2) | mA          |          |

Note 1: Under the CR oscillation mode, when the supply voltage drops below the voltage being generated by the internal constant voltage circuit, the CR oscillation frequency goes down below the prescribed level to reduce the tempo and to bring down the pitch corresponding to the downward deviation of the oscillation frequency. Other circuits function normally under the prescribed specifications.

Note 2 : This value is a reference value, because current consumption varies depending on the programmed pitch, tempo, used notes and address location with each ROM.

### **EPSON**

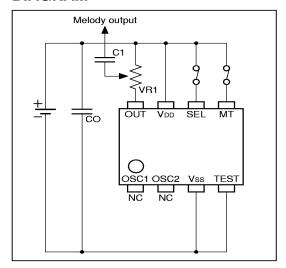

## ■ BASIC EXTERNAL CONNECTION DIAGRAM

#### **■ PACKAGE DIMENSIONS**

#### <Reference circuit constants>

| Symbol | Reference values | Unit    | Remarks                              |

|--------|------------------|---------|--------------------------------------|

| VR1    | more than 1      | МΩ      | Volume controlling variable resistor |

| CO     | 1 to 100         | $\mu$ F | Power stabilizing capacitor          |

| C1     | 0.1              | μF      | Audio output coupling capacitor      |

#### NOTICE:

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, life support products. Morever, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Control Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

© Seiko Epson Corporation 1997 All right reserved.

#### **SEIKO EPSON CORPORATION**

ELECTRONIC DEVICE MARKETING DEPARTMENT

#### IC Marketing & Engineering Group

421-8 Hino, Hino-shi, Tokyo 191, JAPAN Phone: 0425-87-5816 FAX: 0425-87-5624

#### International Marketing Department I (Europe, U.S.A.)

421-8 Hino, Hino-shi, Tokyo 191, JAPAN Phone: 0425-87-5812 FAX: 0425-87-5564

#### International Marketing Department II (Asia)

421-8 Hino, Hino-shi, Tokyo 191, JAPAN Phone: 0425-87-5814 FAX: 0425-87-5110 First issue December, 1994 Printed January, 1997 in Japan §