Bluetooth<sup>®</sup> Smart LSI supporting Core Specification v4.1

#### Overview

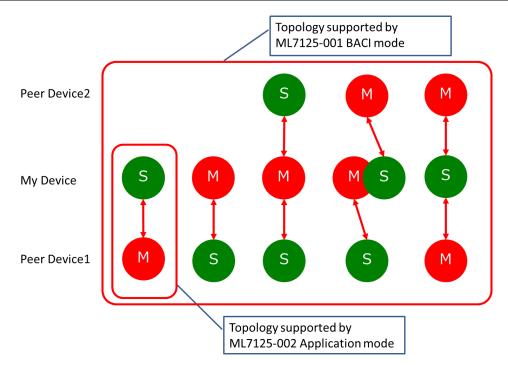

ML7125-00X (-001/-002) is a series of Bluetooth<sup>®</sup> Smart LSI integrating Ultra Low Power RF, Baseband, microproccessor core and peripherals, which has Bluetooth<sup>®</sup> LE compliant 2.4GHz band radio communication capability. ML7125-00X is supporting Bluetooth<sup>®</sup> core specification v4.1, it is suitable for applications such as Wrist Watch, Remote Controller or PC peripherals. The differences in ML7125-00X series are operating mode that is supported by each product.

#### Features

- Bluetooth<sup>®</sup> SIG Core Spec v4.1 compliant, supporting master and slave role function

- Ultra Low Power RF block

- Cortex-M0+ microprocessor core integrated

- 96KB ROM (CODE\_ROM) for Program code. •

- 28KB RAM (CODE/DATA RAM) for user program and data processing

- Memory retention function while the chip is in deep sleep mode with partial power shutdown • (8KB/28KB scalable)

- Bluetooth<sup>®</sup> LE single mode compliant Baseband controller

- 3 Operating modes

- BACI (Bluetooth Application Controller Interface) mode : Lapis original application interface to HOST MCU.\*1

- HCI (Host Controller Interface) mode : Bluetooth<sup>®</sup> standard interface between controller (LL+RF-PHY) and protocol stack.

- Application mode : Download user application into embedded SRAM, two type of application are supported, "Standalone type", "Add-on type". \*2

- Simultaneous connection up to 2 devices. (support all master/slave combinations)\*1

- **UART** interface

- SPI (Slave mode) interface \*1

- I2C (Master & Slave) interface

- GPIO ports

- On chip Regulator Linear regulator (MAIN Regulator) or Switching regulator

- Low Power Operating mode

- Single power supply 1.6V to 3.6V

- **Operating Temperature** -20 deg.C to +75deg.C

- Current Consumptions

- Deep Sleep Mode with external Low Power Clock

- 0.35µA \*3, 0.90µA \*4

- Deep Sleep Mode with internal Low Power Clock oscillator circuit)

#### 2.60µA(TYP) \*3, 3.15µA(TYP) \*4 below 2.0mA(TYP) (Memory retention, 26MHz clock enabled)

- Idle Mode

- below 6.7mA(TYP) (power supply using Switching regulator) Active TX

- Active RX

- below 6.2mA(TYP) (power supply using Switching regulator)

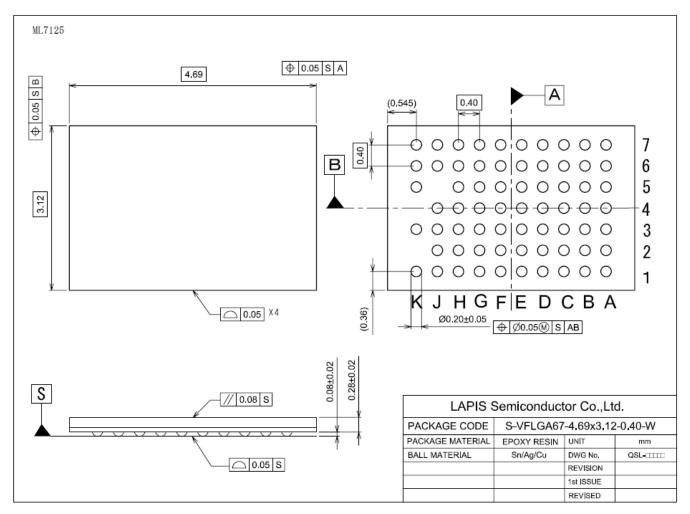

- Package

- 7row x 10column pad WCSP (0.4mm pad pitch LGA type, 4.69 x 3.12) • Pb Free, RoHS compliant

- \*1 : Supported by ML7125-001 only

- \*2 : Supported by ML7125-002 only

- \*3 : APPLICATION RAM no retention

- \*4 : APPLICATION RAM retention

Note : Unless otherwise stated, features listed above supported by both products.(\*1\*2)

## Support Function List

| Function                           | ML7125-001   | ML7125-002                     |  |

|------------------------------------|--------------|--------------------------------|--|

| Role                               | Master/Slave | Slave                          |  |

| Number of connectable<br>device(s) | 2            | 1                              |  |

| BACI Mode                          | 0            | ×                              |  |

| HCI Mode                           | 0            | 0                              |  |

| Application Mode                   | ×            | 0                              |  |

| UART interface                     | 0            | 0                              |  |

| SPI interface                      | 0            | ×                              |  |

| I2C interface                      | 0            | 0                              |  |

| GPIO                               | None         | 4CH                            |  |

| Host interface                     | BACI         | AT-Command<br>(Lapis original) |  |

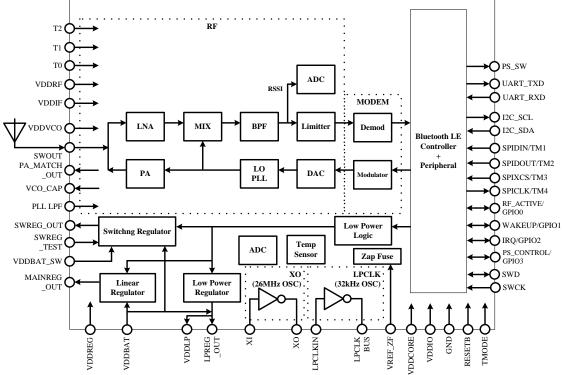

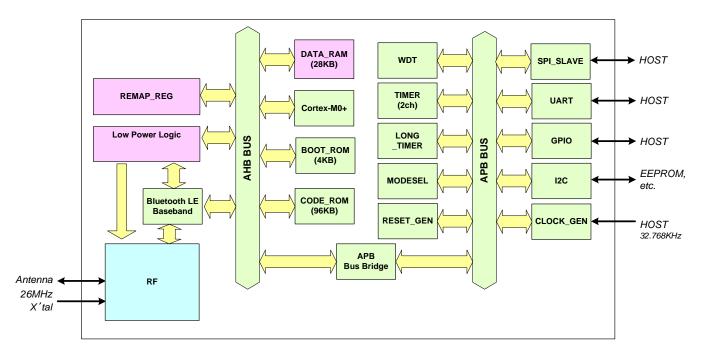

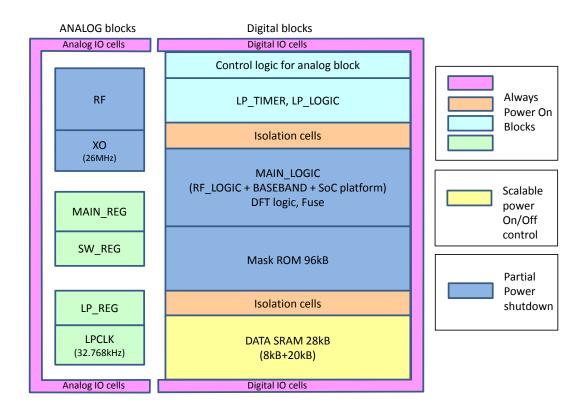

## Block Diagram

1chip overview

Bluetooth<sup>®</sup> LE Platform

## ■ PIN ASSIGNMENT

|   | К                | J       | Н      | G         | F       | Е              | D               | С        | В                    | Α                   |

|---|------------------|---------|--------|-----------|---------|----------------|-----------------|----------|----------------------|---------------------|

| 7 | MAINREG_<br>OUT  | VDDREG  | VDDBAT | LPREG_OUT | VDDIF   | LPCLKIN        | VDDLP           | GND      | SWREG_OUT            | VDDBAT_SW           |

| 6 | GND              | T1      | то     | Т2        | GND     | LPCLKBUS       | RESETB          | TMODE    | SWREG_TEST           | GND                 |

| 5 | SWOUT            | _       | GND    | GND       | GND     | GND            | GND             | GND      | SWD                  | SWCK                |

| 4 | -                | VDDRF   | GND    | GND       | GND     | GND            | GND             | GND      | PS_CONTROL/<br>GPIO3 | IRQ/<br>GPIO2       |

| 3 | PA_MATCH_<br>OUT | VCO_CAP | GND    | GND       | GND     | GND            | GND             | GND      | WAKEUP/<br>GPIO1     | RF_ACTIVE/<br>GPIO0 |

| 2 | _                | VDDVCO  | GND    | GND       | PS_SW   | SPICLK/<br>TM4 | SPIDOUT/<br>TM2 | I2C_SDA  | I2C_SCL              | VDDIO               |

| 1 | PLLLPF           | VDDCORE | XI     | хо        | VREF_ZF | SPIXCS/<br>TM3 | SPIDIN/<br>TM1  | UART_RXD | UART_TXD             | GND                 |

#### BOTTOM VIEW

#### ML7125-001/ML7125-002

## PIN definition

| I/O<br>definitions | I <sub>RF</sub><br>I<br>I <sub>SH</sub><br>I <sub>A</sub><br>I <sub>AH</sub><br>I <sub>SH</sub><br>X <sub>SH</sub><br>X <sub>M</sub><br>O <sub>2</sub><br>B <sub>22</sub> |   | RF input and output<br>Digital input<br>Low-Power Clock input<br>Digital input with pull-down resistor<br>Analog input<br>Analog input support 3V<br>Low-Power Clock input<br>X'tal pin for Low-Power Clock<br>X'tal pin for Master Clock<br>Digital output with 2mA load capability<br>Digital input with 2mA load capability |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | B2pd                                                                                                                                                                      | : | Digital inout with 2mA load capability with pull-down resistor                                                                                                                                                                                                                                                                 |

|                    | OA                                                                                                                                                                        | : | Analog output                                                                                                                                                                                                                                                                                                                  |

## • RF analog pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O              | Active<br>Level | Function                       |

|----|------------------------|------------------------|-----------------|------------------|-----------------|--------------------------------|

| K5 | SWOUT                  | *1                     | Hi-Z            | I <sub>RF</sub>  |                 | RF signal RX/TX inout          |

| H6 | ТО                     | *1                     | Hi-Z            | I <sub>AH</sub>  |                 | Test input signal              |

| J6 | T1                     | *1                     | Hi-Z            | I <sub>AH,</sub> |                 | Test input signal              |

| G6 | T2                     | *1                     | Hi-Z            | I <sub>AH,</sub> |                 | Test input signal              |

| K1 | PLLLPF                 | *1                     | Hi-Z            | OA               |                 | PLL Loop Filter                |

| КЗ | PA_MATCH_<br>OUT       | *1                     |                 |                  |                 | Output for PA matching circuit |

| J3 | VCO_CAP                | *1                     |                 |                  |                 | Output for VCO capacitor       |

\*1: Same as ML7125-001

## • XO, LPCLK pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O              | Active<br>Level | Function                                    |

|----|------------------------|------------------------|-----------------|------------------|-----------------|---------------------------------------------|

| H1 | XI                     | *1                     | Hi-Z            | X <sub>M</sub>   |                 | Input pin for Master clock oscillator block |

| G1 | XO                     | *1                     | Hi-Z            | X <sub>M</sub>   |                 | Outputpin for Master clock oscillator block |

| E6 | LPCLKBUS               | *1                     | 0V              | X <sub>SH</sub>  |                 | Low power clock Xtal output                 |

| E7 | LPCLKIN                | *1                     | I <sub>SH</sub> | $X_{SH}, I_{SH}$ |                 | Low power clock/Xtal input                  |

\*1: Same as ML7125-001

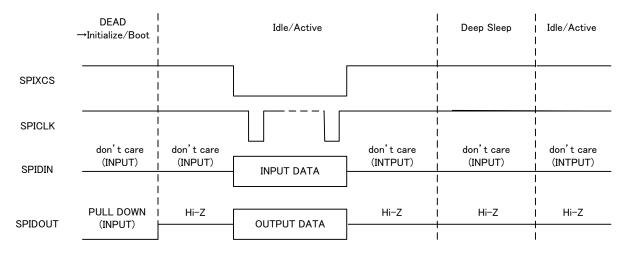

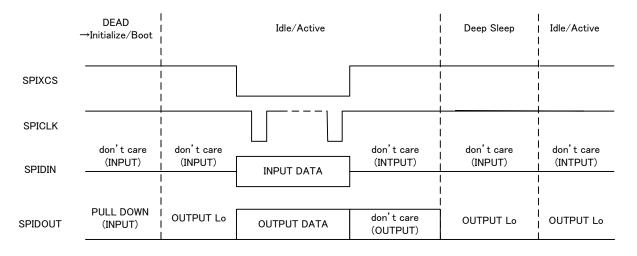

• SPI pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O  | Active<br>Level | Function                                                            |

|----|------------------------|------------------------|-----------------|------|-----------------|---------------------------------------------------------------------|

| D1 | SPIDIN                 | TM1                    | Input           | I    |                 | SPIDIN : SPI SLAVE Data input<br>TM1 : Test mode definition input   |

| D2 | SPIDOUT                | TM2                    | Input           | B2pd |                 | SPIDOUT : SPI SLAVE Data output<br>TM2 : Test mode definition input |

| E1 | SPIXCS                 | TM3                    | Input           | Ι    | Low             | SPIXCS : SPI SLAVE Chip Select<br>TM3 : Test mode definition input  |

#### ML7125-001/ML7125-002

| E2 | SPICLK | TM4 | Input | I | <br>SPICLK : SPI SLAVE Clock<br>TM4 : Test mode definition input |

|----|--------|-----|-------|---|------------------------------------------------------------------|

## • UART pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O            | Active<br>Level | Function        |

|----|------------------------|------------------------|-----------------|----------------|-----------------|-----------------|

| B1 | UART_TXD               | *1                     | High output     | O <sub>2</sub> |                 | UART TXD output |

| C1 | UART_RXD               | *1                     | input           | B2pd           |                 | UART RXD input  |

\*1: Same as ML7125-001

## • I2C pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O | Active<br>Level | Function |

|----|------------------------|------------------------|-----------------|-----|-----------------|----------|

| B2 | I2C_SCL                | *1                     | Input           | B2  |                 | I2C_SCL  |

| C2 | I2C_SDA                | *1                     | Input           | B2  |                 | I2C_SDA  |

\*1: Same as ML7125-001

## • GPIO pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O | Active<br>Level | Function                                                                                          |

|----|------------------------|------------------------|-----------------|-----|-----------------|---------------------------------------------------------------------------------------------------|

| A3 | RF_ACTIVE              | GPIO0                  | Low output      | B2  |                 | RF_ACTIVE : Status pin indicates RF access<br>activity.<br>GPIO0 : GPIO inout                     |

| В3 | WAKEUP                 | GPIO1                  | Input           | B2  |                 | WAKEUP : Control pin from HOST to wakeup<br>ML7125-001<br>GPIO1 : GPIO inout/                     |

| A4 | IRQ                    | GPIO2                  | High output     | B2  |                 | IRQ : Status pin indicates interruption reason taken<br>place in ML7125-001<br>GPIO2 : GPIO inout |

| B4 | PS_CONTRO<br>L         | GPIO3                  | Low output      | B2  |                 | PS_CONTROL : Status pin indicates deep sleep<br>mode status.<br>GPIO3 : GPIO inout                |

## • Debugger pins

| No   | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O | Active<br>Level | Function        |

|------|------------------------|------------------------|-----------------|-----|-----------------|-----------------|

| B5   | SWD                    | *1                     | input           | B2  |                 | SWD data inout  |

| A5   | SWCK                   | *1                     | input           | l   |                 | SWD clock input |

| 14.0 |                        |                        |                 |     |                 |                 |

\*1: Same as ML7125-001

## • Miscellaneous pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O | Active<br>Level | Function |

|----|------------------------|------------------------|-----------------|-----|-----------------|----------|

|----|------------------------|------------------------|-----------------|-----|-----------------|----------|

## ML7125-001/ML7125-002

| D6 | RESETB  | *1 | input  | I <sub>S</sub> | Low | Reset input (Low = Reset)                                                 |

|----|---------|----|--------|----------------|-----|---------------------------------------------------------------------------|

| F1 | VREF_ZF | *1 |        |                |     | Test input (fix to low)                                                   |

| C6 | TMODE   | *1 | input  | I              |     | TESTMODE input (Low = normal mode)                                        |

| F2 | PS_SW   | *1 | output | O <sub>2</sub> |     | Status pin indicates deep sleep mode status.<br>(Control for Powe switch) |

\*1: Same as ML7125-001

• Regulator pins

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset     | I/O | Active<br>Level | Function                                                                                       |

|----|------------------------|------------------------|---------------------|-----|-----------------|------------------------------------------------------------------------------------------------|

| K7 | MAINREG_OU<br>T        | *1                     | 1.35V<br>output     |     |                 | Linear Regulator output<br>Note) please do not shortcut this pin to GND, IC<br>may be damaged. |

| G7 | LPREG_OUT              | *1                     | 0.90V<br>output     |     |                 | Low Power Regulator output                                                                     |

| B7 | SWREG_OUT              | *1                     | 1.35V<br>output     |     |                 | Switching Regulator output                                                                     |

| J7 | VDDREG                 | *1                     | 1.35V/3.3V<br>input |     |                 | Feedback input for Switching Regulator and Power<br>supply input for Linear Regulator.         |

| B6 | SWREG_TES<br>T         | *1                     |                     |     |                 | Switching Regulator test pin                                                                   |

\*1: Same as ML7125-001

## • Power Supply pin

| No | Pin Name<br>ML7125-001 | Pin Name<br>ML7125-002 | Status in reset | I/O | Active<br>Level | Function                                          |

|----|------------------------|------------------------|-----------------|-----|-----------------|---------------------------------------------------|

| A7 | VDDBAT_SW              | *1                     |                 |     |                 | Power supply from Battery (=VDDIO) (1.6V to 3.6V) |

| H7 | VDDBAT                 | *1                     |                 |     |                 | Power supply from Battery (=VDDIO) (1.6V to 3.6V) |

| A2 | VDDIO                  | *1                     |                 |     |                 | Power supply for digital IO (1.6V to 3.6V)        |

| J4 | VDDRF                  | *1                     |                 |     |                 | Power supply for RF block (1.35V)                 |

| F7 | VDDIF                  | *1                     |                 |     |                 | Power supply for IF block (1.35V)                 |

| J2 | VDDVCO                 | *1                     |                 |     |                 | Power supply for RF-VCO (1.35V)                   |

| J1 | VDDCORE                | *1                     |                 |     |                 | Power supply for digital core (1.35V)             |

| D7 | VDDLP                  | *1                     |                 |     |                 | Power supply for low power digital core (1.35V)   |

| C7 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| K6 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| F6 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| A6 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| H5 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| G5 | GND                    | *1                     |                 |     |                 | GND                                               |

| F5 | GND                    | *1                     |                 |     |                 | GND                                               |

| E5 | GND                    | *1                     |                 |     |                 | GND                                               |

| D5 | GND                    | *1                     |                 |     |                 | GND                                               |

| C5 | GND                    | *1                     |                 |     |                 | GND                                               |

| H4 | GND                    | *1                     |                 |     |                 | GND (Mandatory)                                   |

| G4 | GND                    | *1                     |                 |     |                 | GND                                               |

| F4 | GND                    | *1                     |                 |     |                 | GND                                               |

#### ML7125-001/ML7125-002

| E4 | GND | *1 | <br> | <br>GND             |

|----|-----|----|------|---------------------|

| D4 | GND | *1 | <br> | <br>GND             |

| C4 | GND | *1 | <br> | <br>GND             |

| H3 | GND | *1 | <br> | <br>GND (Mandatory) |

| G3 | GND | *1 | <br> | <br>GND             |

| F3 | GND | *1 | <br> | <br>GND             |

| E3 | GND | *1 | <br> | <br>GND             |

| D3 | GND | *1 | <br> | <br>GND             |

| C3 | GND | *1 | <br> | <br>GND             |

| H2 | GND | *1 | <br> | <br>GND (Mandatory) |

| G2 | GND | *1 | <br> | <br>GND (Mandatory) |

| A1 | GND | *1 | <br> | <br>GND (Mandatory) |

|    |     |    |      |                     |

\*1: Same as ML7125-001

## • Unused pins

Followings are recommendation for pins are not used.

| No | Pin Name         | Recommendation                                     |

|----|------------------|----------------------------------------------------|

| E6 | LPCLKBUS         | Open                                               |

| K1 | PLLLPF           | Open (Optionally, PLL loop filter may be required) |

| F1 | VREF_ZF          | Fix to GND                                         |

| D1 | SPIDIN/TM1       | Fix to VDDIO                                       |

| D2 | SPIDOUT/TM2      | Open                                               |

| E1 | SPIXCS/TM3       | Fix to VDDIO                                       |

| E2 | SPICLK/TM4       | Fix to VDDIO                                       |

| B1 | UART_TXD         | Open                                               |

| C1 | UART_RXD         | Fix to GND (See operating mode section)            |

| B2 | I2C_SCL          | Fix to VDDIO                                       |

| C2 | I2C_SDA          | Fix to GND                                         |

| A3 | RF_ACTIVE/GPIO0  | Open                                               |

| B3 | WAKEUP/GPIO1     | Fix to VDDIO or GND (See operating mode section)   |

| A4 | IRQ/GPIO2        | Open                                               |

| B4 | PS_CONTROL/GPIO3 | Open                                               |

| F2 | PS_SW            | Open                                               |

| H6 | ТО               | Open                                               |

| B5 | SWD              | Fix to GND                                         |

| A5 | SWCK             | Fix to GND                                         |

| J6 | T1               | Open                                               |

| G6 | T2               | Open                                               |

#### Note

Leaving input pins open with Hi-Z status, current consumption will be increased. It is highly recommended that input or in-out pins should not be left open.

#### ML7125-001/ML7125-002

## Electrical Characteristics

## • Absolute Maximum Rating

| Item                             | Symbol           | Condition             | Rating             | Unit  |

|----------------------------------|------------------|-----------------------|--------------------|-------|

| Power supply 3.3V (*1)           | Vddhv1<br>Vddhv2 |                       | -0.3 to +4.6       | V     |

| Power supply 1.35V (*2)          | Vddlv            |                       | -0.3 to +1.8       | V     |

| Digital input voltage (*4)       | Vdin             |                       | -0.3 to VDDHV*+0.3 | V     |

| Digital output voltage (*5)      | Vdo              | Ta = -20 to +75 deg.C | -0.3 to VDDHV*+0.3 | V     |

| Analog IO voltage (*6)           | VA               | GND= 0 V (*3)         | -0.3 to VDDLV+0.3  | V     |

| Analog HV IO voltage (*7)        | Vah              | VDDRF=VDDVCO          | -0.3 to VDDHV*+0.3 | V     |

| Digital IO load current (*4)(*5) | Ido              | =VDDCORE,             | -10 to +10         | mA    |

| Analog IO current (*6)(*7)       | IA               | VDDBAT= VDDBAT _SW,   | -2 to +2           | mA    |

| Power Dissipation                | PD               | =VDDIO,               | 1.0                | W     |

| Storage temperature              | Tstg             | _                     | -55 to +125        | deg.C |

(\*1) VDDBAT, VDDBAT\_SW, VDDIO pins (\*2) VDDRF, VDDVCO, VDDCORE,

(\*3) GND pin (Package GND)

(\*4) IO pins with I, IPD, B2 symbol in pin definition

(\*5) IO pins with O<sub>2</sub>, B<sub>2</sub>, B<sub>2pd</sub> symbol in pin definition

(\*6) IO pins with IA, OA, X<sub>M</sub> symbol in pin definition (\*7) IO pins with IAH,  $I_{SH}$ ,  $X_{SH}$ , symbol in pin definition

## • Recommended Operating Conditions

| Item                                                            | Symbol           | Condition                                                      | Min         | Тур    | Max         | Unit |

|-----------------------------------------------------------------|------------------|----------------------------------------------------------------|-------------|--------|-------------|------|

| Power Supply                                                    | Vddhv1           | VDDIO pin<br>(VDDBAT, VDDBAT_SW≧<br>VDDIO)                     | 1.60        | 3.00   | 3.60        | V    |

| Power Supply<br>(Linear Regulator used)                         | VDDHV2_1         | VDDBAT,VDDBAT_SW pin<br>(VDDBAT, VDDBAT_SW≧<br>VDDIO)          | 1.60        | 3.00   | 3.60        | V    |

| Power Supply<br>(Switching Regulator used)                      | Vddhv2_2         | VDDBAT,VDDBAT_SW pin<br>(VDDBAT, VDDBAT_SW≧<br>VDDIO)          | 2.00        | 3.00   | 3.60        | V    |

| Power Supply                                                    | VDDLCV1          | VDDCORE pin                                                    | 1.25        | 1.35   | 1.55        | V    |

| (IDLE/RF_ACTIVE)                                                | VDDLRV1          | VDDRF pin,<br>VDDVCO pin                                       | 1.25        | 1.35   | 1.55        | V    |

| Power Supply                                                    | VDDLCV2          | VDDCORE pin                                                    | 0.70        | 0.90   | 1.00        | V    |

| (Deep Sleep)                                                    | Vddlrv2          | VDDRF pin,<br>VDDVCO pin                                       | -           | Hi-Z   | -           | V    |

| Ambient Temperature                                             | Ta               | _                                                              | -20         | +25    | +75         | °C   |

| Rising time digital input pins                                  | t <sub>IR1</sub> | Digital input pins                                             | _           | -      | 20          | ns   |

| Falling time digital input pins                                 | t <sub>IF1</sub> | Digital input pins                                             | _           | _      | 20          | ns   |

| Load capacitance digital                                        | CDL              | Digital output pins                                            | _           | -      | 20          | pF   |

| Master Clock (26 MHz)<br>crystal oscillator frequency           | <b>F</b> мск1    | Connect cristal oscillator<br>between XI-XO pins<br>(*1), (*2) | –40<br>ppm  | 26     | +40<br>ppm  | MHz  |

| Low Power Clock<br>(32.768 kHz)<br>crystal oscillator frequency | FLPCK1           | LPCLKIN pin,<br>LPCLKBUS pin (*2)                              | –500<br>ppm | 32.768 | +500<br>ppm | kHz  |

| Low Power Clock<br>Input Duty Ratio                             | DLPCK1           | External input from LPCLKIN, LPCLKBUS pin left OPEN            | 30          | 50     | 70          | %    |

| RF Channel frequency (*3)                                       | Frf              | SWOUT pin                                                      | 2402        | _      | 2480        | MHz  |

| RF input level                                                  | Prfin            |                                                                | -70         | -      | -10         | dBm  |

(\*1) Cristal oscillator is recommended

(\*2) The cristal should be used the one that meet the specification include peripheral circuit. (\*3) Frequency range  $F = 2402 + 2 \times k \text{ [MHz]}$  here k=0, 1,2,...,39.

## • Current consumption

#### <<Linear Regulator case >>

|                     |          |                                                              |     | (Ta  | = -20 to + | 75 deg.C) |

|---------------------|----------|--------------------------------------------------------------|-----|------|------------|-----------|

| Item                | Symbol   | Condition                                                    | Min | Тур  | Max        | Unit      |

|                     | IDD_DSM1 | Deep Sleep State (External<br>Low Power Clock) *1            |     | 0.35 |            | μA        |

|                     | IDD_DSM2 | Deep Sleep State (Internal Low<br>Power Clock oscillator) *1 |     | 2.60 |            | μA        |

|                     | IDD_IDLE | Idle State                                                   |     | 3.2  |            | mA        |

|                     | IDD_RX1  | RF RX State (High Sense<br>Mode)                             |     | 10.8 |            | mA        |

| Current Consumption | IDD_RX2  | RF RX State (Mid Sense Mode)                                 |     | 10.5 |            | mA        |

|                     | IDD_RX3  | RF RX State (Low Sense<br>Mode)                              |     | 10.0 |            | mA        |

|                     | IDD_TX1  | RF TX State (TX power at +4dBm)                              |     | 17.1 |            | mA        |

|                     | IDD_TX2  | RF TX State (TX power at<br>0dBm)                            |     | 11.4 |            | mA        |

|                     | IDD_TX3  | RF TX State (TX power at -18dBm)                             |     | 7.4  |            | mA        |

\*1 Additional  $0.55\mu A$  required in case of APPLICATION RAM retention

<<Switching Regulator case >>

|                     |          |                                                              |     | (Ta  | = -20 to + | 75 deg.C) |

|---------------------|----------|--------------------------------------------------------------|-----|------|------------|-----------|

| Item                | Symbol   | Condition                                                    | Min | Тур  | Max        | Unit      |

|                     | IDD_DSM1 | Deep Sleep State (External<br>Low Power Clock) *1            |     | 0.35 |            | μA        |

|                     | IDD_DSM2 | Deep Sleep State (Internal Low<br>Power Clock oscillator) *1 |     | 2.60 |            | μA        |

|                     | IDD_IDLE | Idle State                                                   |     | 2.0  |            | mA        |

|                     | IDD_RX1  | RF RX State (HighSense<br>Mode)                              |     | 6.4  |            | mA        |

| Current Consumption | IDD_RX2  | RF RX State (Mid Sense Mode)                                 |     | 6.2  |            | mA        |

|                     | IDD_RX3  | RF RX State (Low Sense<br>Mode)                              |     | 5.8  |            | mA        |

|                     | IDD_TX1  | RF TX State (TX power at<br>+4dBm)                           |     | 10.3 |            | mA        |

|                     | IDD_TX2  | RF TX State (TX power at<br>0dBm)                            |     | 6.7  |            | mA        |

|                     | IDD_TX3  | RF TX State (TX power at -18dBm)                             |     | 4.3  |            | mA        |

\*1 Additional 0.55µA required in case of APPLICATION RAM retention

### • DC characteristics

|                                      |           |                                                           |               | (Ta  | = -20 to +7     | 75 deg.C) |

|--------------------------------------|-----------|-----------------------------------------------------------|---------------|------|-----------------|-----------|

| Item                                 | Symbol    | Condition                                                 | Min           | Тур  | Max             | Unit      |

| H level Voltage Input                | VIH1      | (*1) (*2) (*5) (*6)                                       | Vddio<br>X0.7 | Ι    | Vddio           | V         |

| L level Voltage input                | VIL1      | (*1) (*2) (*5) (*6)                                       | 0             | _    | Vddio<br>X0.3   | V         |

| LPCLKIN pin<br>H level Voltage Input | VIH2      | (*3)                                                      | 1             | μ    | Vddio           | V         |

| LPCLKIN pin<br>L level Voltage input | VIL2      | (*3)                                                      | 0             | Ι    | 0.3             | V         |

|                                      | IIH1      | VIH = VDDIO (*1) (*5)                                     | -1            | -    | 1               | μA        |

| Input leak current                   | Іін2      | VIH = VDDIO (*2)(*6)                                      | 5             | -    | 250             | μA        |

|                                      | IIL1      | VIL = 0 V (*1) (*2) (*5)(*6)                              | -1            | -    | 1               | μA        |

| Tri-state output leak                | Іоzн      | Voh = Vddio (*4) (*5)                                     | -1            | -    | 1               | μA        |

| current                              | Iozl      | VOL = 0 V (*4) (*5)                                       | -1            | -    | 1               | μA        |

|                                      | VOH1      | IOH = -2mA (*4) (*5)(*6)<br>VDDIO = VDDBAT = 2.0V to 3.6V | VDDIO × 0.75  | -    | Vddio           | V         |

| H level Voltage Output               | Vон2      | IOL = -1mA (*4) (*5)(*6)<br>VDDIO = VDDBAT = 1.6V to 2.0V | VDDIO × 0.65  | _    | Vddio           | V         |

| L level Voltage Output               | Vol1      | IOH = 2mA (*4) (*5)(*6)<br>VDDIO = VDDBAT = 2.0V to 3.6V  | 0             | _    | VDDIO × 0.25    | V         |

|                                      | Vol2      | IOL = 2mA (*4) (*5)(*6)<br>VDDIO = VDDBAT = 1.6V to 2.0V  | 0             | -    | VDDIO ×<br>0.35 | V         |

|                                      | VMAIN_OUT | MAINREG_OUT pin                                           | 1.25          | 1.35 | 1.55            | V         |

| Regulator output voltage             | Vsw_out   | SWREG_OUT pin                                             | 1.25          | 1.35 | 1.55            | V         |

|                                      | VLP_OUT   | LPREG_OUT pin                                             | 0.70          | 0.90 | 1.10            | V         |

| Input pin capacitance                | CIN       | F=1MHz (*1) (*2) (*4) (*5)                                | _             | 8    | -               | pF        |

(\*1) IO pins with I symbol in pin definition

(\*2) IO pins with IPD symbol in pin definition

(\*3) IO pins with ISH symbol in pin definition

(\*4) IO pins with O2 symbol in pin definition

(\*5) IO pins with B2 symbol in pin definition

(\*6) IO pins with B2pd symbol in pin definition

## • RF Characteristics

| ltom                                                       | Sumbol             | Condition                                                              | Min  |      | = -20  to  + | <u> </u> |

|------------------------------------------------------------|--------------------|------------------------------------------------------------------------|------|------|--------------|----------|

| Item                                                       | Symbol             | Condition                                                              | Min  | Тур  | Max          | Unit     |

| ТХ                                                         | _                  |                                                                        |      |      |              |          |

|                                                            | P <sub>OUT1</sub>  | TX- 4dBm setting *1                                                    |      | 4    | _            | dBm      |

| TX power                                                   | Pout2              | TX- 0dBm setting                                                       | -    | 0    | -            | dBm      |

|                                                            | P <sub>OUT3</sub>  | TX18dBm setting                                                        | -    | -18  | -            | dBm      |

|                                                            | P <sub>STEP1</sub> | The number of power control step in TX-Normal mode                     | _    | 4    | _            | Step     |

| TX power control                                           | P <sub>STEP2</sub> | Power control step gain in<br>TX-Normal mode                           | _    | 6    | _            | dB       |

| Centre Frequency tolerance                                 | F <sub>CERR</sub>  | Master Clock tolerance < 40<br>ppm                                     | -40  | 0    | 40           | Ppm      |

| Modulation data rate                                       | D <sub>RATE</sub>  | -                                                                      | _    | 1    | _            | Mbps     |

| Modulation index                                           | F <sub>IDX</sub>   | -                                                                      | 0.45 | 0.50 | 0.55         | -        |

| Bandwidth-bit rate<br>products BT                          | BT                 | GFSK                                                                   | _    | 0.5  | _            | _        |

|                                                            | $F_{1avg}$         | Frequency deviation of 10101010 pattern                                | 225  | 250  | 275          | kHz      |

| Modulation<br>characteristics                              | F <sub>RATE</sub>  | Frequency deviation ratio<br>between 10101010 and<br>00001111 sequence | 80   | _    | _            | %        |

|                                                            | FDELTA             | Minimum Frequency Deviation                                            | 185  | _    | _            | kHz      |

|                                                            | P <sub>OS1</sub>   | 2MHz apart from carrier<br>frequency in a 1MHz bandwidth               | _    | _    | -20          | dBm      |

| In-band spurious                                           | P <sub>OS2</sub>   | 3MHz apart from carrier frequency in a 1MHz bandwidth                  | _    | _    | -30          | dBm      |

| Out-band spurious                                          | P <sub>OB</sub>    | ARIB STD-T66<br>(RBW=VBW=100kHz)                                       | _    | _    | -26          | dBm      |

| Ramping Up/Down                                            | T <sub>RMP</sub>   | Time required for Ramping up and Ramping down                          | 0    | 2    | 8            | μS       |

| RX                                                         |                    |                                                                        |      |      |              |          |

|                                                            | P <sub>SENS1</sub> | PER = 30.8%<br>(High Sense Mode)                                       | _    | -88  | -70          | dBm      |

| Receiver Sensitivity                                       | $P_{SENS2}$        | PER = 30.8%<br>(Mid Sense Mode)                                        | _    | -85  | -70          | dBm      |

|                                                            | P <sub>SENS3</sub> | PER = 30.8%<br>(Low Sense Mode)                                        | _    | _    | -70          | dBm      |

| Interference performance                                   | Cl <sub>co</sub>   | Co-channel interference C/I                                            | 21   | _    | _            | dB       |

| PER<30.8%<br>Wanted signal :-67dBm<br>Interfering signal : | CI <sub>S1</sub>   | Adjacent (1MHz) interference<br>C/I                                    | 15   | _    | _            | dB       |

| modulated signal<br>(1*)(*2)(*3)                           | CI <sub>S2</sub>   | Adjacent (2MHz) interference<br>C/I                                    | -17  | _    | _            | dB       |

| ( ) 2) 3)                                                  | CI <sub>S3</sub>   | Adjacent (>=3MHz)<br>interference C/I                                  | -27  | -    | -            | dB       |

#### ML7125-001/ML7125-002

|                                                                   | CI <sub>IMG</sub>    | Image frequency interference<br>(-4MHz) C/I                                                                                                                                                                                                  | -9  | - | -   | dB  |

|-------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---|-----|-----|

|                                                                   | CI <sub>IMGS1</sub>  | Adjacent (1MHz) interference<br>to image frequency<br>(-3MHz,-5MHz)) C/I                                                                                                                                                                     | -15 | - | -   | dB  |

| Out of band blocking                                              | P <sub>BLK1</sub>    | 30MHz to 2000MHz BW<br>10MHz                                                                                                                                                                                                                 | -30 | - | -   | dBm |

| PER<30.8%<br>Wanted signal :-67dBm                                | P <sub>BLK2</sub>    | 2003 to 2399MHz BW 3MHz                                                                                                                                                                                                                      | -35 | _ | _   | dBm |

| Interfering signal:CW                                             | P <sub>BLK3</sub>    | 2484 to 2997MHz BW 3MHz                                                                                                                                                                                                                      | -35 | _ | _   | dBm |

| Interfering signal:CW<br>(*1) (*2) (*3)                           | P <sub>BLK4</sub>    | 3000MHz to 12.75GHz BW<br>25MHz                                                                                                                                                                                                              | -30 | _ | _   | dBm |

| Intermodulation<br>PER<30.8%<br>Wanted signal :-64dBm<br>(*1)(*3) | Рім                  | CW interering signal +/-3MHz<br>Modulated interfering signal<br>+/-6MHz<br>or<br>CW interfering signal +/-4MHz<br>Modulated interfering signal<br>+/-8MHz<br>or<br>CW interfering signal +/-5MHz<br>Modulated interfering signal<br>+/-10MHz | -50 | _ | _   | dBm |

| Spurious Emission level                                           | P <sub>SPR1</sub>    | 30 MHz $\sim$ 1 GHz<br>(RBW=VBW=100kHz)                                                                                                                                                                                                      | Ι   | - | -54 | dBm |

| (ARIB STD-T66)                                                    | P <sub>SPR2</sub>    | 1 GHz $\sim$ 12.75 GHz<br>(RBW=VBW=100kHz)                                                                                                                                                                                                   | _   | - | -47 | dBm |

| Maximum input level(*1)                                           | P <sub>RXMAX</sub>   | PER = 30.8% (*1)                                                                                                                                                                                                                             | _   | - | -10 | dBm |

| RSSI detection range                                              | P <sub>RSSIMAX</sub> | Upper                                                                                                                                                                                                                                        | -40 | _ | _   | dBm |

| (*1)(*3)                                                          | PRSSIMIN             | Lower                                                                                                                                                                                                                                        | _   | _ | -85 | dBm |

(\*1) Condition: Ta = 25deg., VDDHV1 = VDDHV2= 3.0V(\*2) Follow RCV-LE/CA/04/C test spec of Bluetooth SIG

(\*3) exclude Low Sense Mode

|                     |                       |                             |      | (Ta  | = -20 to + | 75 deg.C) |  |  |

|---------------------|-----------------------|-----------------------------|------|------|------------|-----------|--|--|

| Item                | Symbol                | Condition                   | Min  | Тур  | Max        | Unit      |  |  |

| Internal Regulator  |                       |                             |      |      |            |           |  |  |

|                     | V <sub>REG1IN</sub>   | Linear Regulator is used    | 1.60 | 3.00 | 3.60       | V         |  |  |

| Input Voltage Range | V <sub>REG2IN</sub>   | Switching Regulator is used | 2.00 | 3.00 | 3.60       | V         |  |  |

| <b>2</b>            | V <sub>REG2OUT1</sub> | Idle, Active mode           | 1.25 | 1.35 | 1.55       | V         |  |  |

| Output Voltage      | V <sub>REG2OUT1</sub> | Deep Sleep mode             | 0.85 | 0.90 | 0.95       | V         |  |  |

| Output load current | I <sub>REG2OUT</sub>  |                             | 8    | 10   | -          | mA        |  |  |

| Start up time       | T <sub>REG2</sub>     |                             | -    | -    | 200        | μS        |  |  |

| Low-Power Regulator |                       |                             |      |      |            |           |  |  |

| Input Voltage Range | V <sub>LPREGIN</sub>  |                             | 1.60 | 3.00 | 3.60       | V         |  |  |

| Output Voltage      | V <sub>LPREGOUT</sub> | Partial down, Sleep mode    | 0.70 | 0.90 | 1.10       | V         |  |  |

| Output load current | I <sub>LPREGOUT</sub> |                             | 8    | 10   | -          | μA        |  |  |

| Start up time       | T <sub>LPREG</sub>    |                             | -    | 5    | _          | ms        |  |  |

## Analog Characteristics • Regulators

## • Analog Characteristics • Miscellaneous

| Item                           | Symbol              | Condition | Min   | Тур | Max  | Unit     |  |  |  |

|--------------------------------|---------------------|-----------|-------|-----|------|----------|--|--|--|

| Temperature Sensor             | Temperature Sensor  |           |       |     |      |          |  |  |  |

| Detection Range                | T <sub>RANGE</sub>  |           | -20   | -   | 75   | °C       |  |  |  |

| Relative Detection<br>Accuracy | T <sub>SLOPE</sub>  |           | -4    | -5  | -6   | °C /code |  |  |  |

| Battery Monitor                |                     |           |       |     |      |          |  |  |  |

| Detection Range                | V <sub>BRANGE</sub> |           | 1.6   | -   | 3.6  | V        |  |  |  |

| Detection Accuracy             | V <sub>BACC</sub>   |           | -0.05 | _   | 0.05 | V        |  |  |  |

#### ML7125-001/ML7125-002

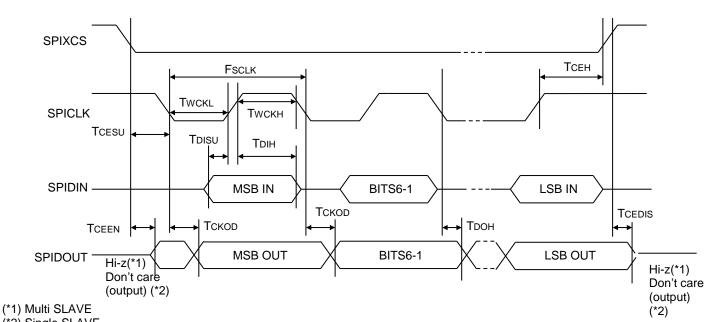

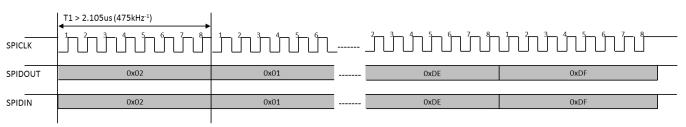

### • SPI interface

SPI block is available to use only ML7125-001

|                                    | (Ta = -20 to +75 deg.0 |                  |         |        |        |      |  |  |

|------------------------------------|------------------------|------------------|---------|--------|--------|------|--|--|

| Item                               | Symbol                 | Condition        | Min     | Тур    | Max    | Unit |  |  |

| SPICLK Clock Frequency             | FSCLK                  |                  | 16.384  | 32.768 | 1625*1 | kHz  |  |  |

| SPIXCS input setup time            | TCESU                  |                  | 1/Fsclk | -      | -      | ms   |  |  |

| SPIXCS input hold time             | Тсен                   |                  | 1/Fsclk | -      | -      | ms   |  |  |

| SPICLK minimum high<br>pulse width | Тwскн                  |                  | 250     | -      | -      | ns   |  |  |

| SPICLK minimum low<br>pulse width  | Тwcкl                  |                  | 250     | -      | -      | ns   |  |  |

| SPIDIN input setup time            | TDISU                  | Load capacitance | 5       | -      | -      | ns   |  |  |

| SPIDIN input hold time             | Тон                    | CL=20pF          | 250     | Ι      | -      | ns   |  |  |

| SPICLK output delay time           | Тскор                  |                  | -       | -      | 250    | ns   |  |  |

| SPIDOUT output hold time           | Трон                   |                  | 5       | -      | -      | ns   |  |  |

| SPIXCS enable delay time           | TCEEN                  |                  | 0       | -      | 300    | ns   |  |  |

| SPIXCS disable delay time          | TCEDIS                 |                  | 150     | -      | -      | ns   |  |  |

Note: When using the width of the following SPICLK edge from the data output trigger SPICLK edge within 250 ns, there is possibility that the output timing of SPIDOUT becomes simultaneous with the following edge. Consider the data input setup time of HOST and set pulse width.

\*1 : Practical maximum SPICLK clock frequency is limited to 475kHz when multiple bytes of data are transmitted consecutively without time interval between each byte transfer.

Remarks: All timing specification is defined at VDDIO x 20% and VDDIO x 80% SPIXCS input setup/hold time have to be at least 1cycle of SPICLK clock frequency

Measurement point

FEDL7125-04

## LAPIS Semiconductor Co., Ltd.

#### ML7125-001/ML7125-002

(\*2) Single SLAVE

No Time interval between byte transfer (t=0)

Time interval between byte transfer (t>0)

|         | T1 > 16.8us (475kHz <sup>-1</sup> x8) | <u> </u>  | 8 1 2 3 4 5 6 7 8 |

|---------|---------------------------------------|-----------|-------------------|

| SPICLK  |                                       |           |                   |

| SPIDOUT | 0x02                                  | 0x01 0xDE | 0xDF              |

| SPIDIN  | 0x02                                  | 0x01 0xDE | 0xDF              |

| SPICLK frequency [kHz] | T1 : transmit 1byte data [us] | Minimum Time interval t [us] |

|------------------------|-------------------------------|------------------------------|

| 475                    | 16.8                          | 0.0                          |

| 512                    | 15.6                          | 1.2                          |

| 1000                   | 8.0                           | 8.8                          |

| 1600                   | 5.0                           | 11.8                         |

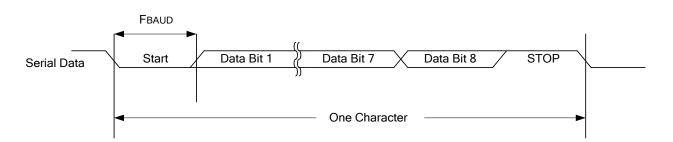

## • UART interface

|           |        |                             |     | (Ta   | = -20 to + | 75 deg.C) |

|-----------|--------|-----------------------------|-----|-------|------------|-----------|

| Item      | Symbol | Condition                   | Min | Тур   | Max        | Unit      |

| Baud Rate | FBAUD  | Load capacitance<br>CL=20pF | -   | 57600 | -          | bps(Hz)   |

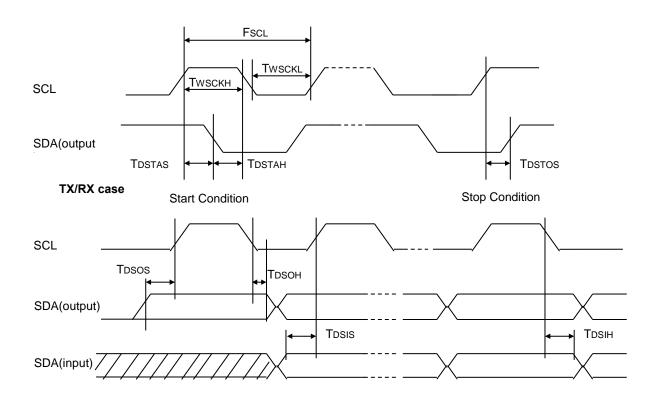

### • I2C interface

|                              |        |                  |     | (Ta | = -20 to + | 75 deg.C) |

|------------------------------|--------|------------------|-----|-----|------------|-----------|

| Item                         | Symbol | Condition        | Min | Тур | Max        | Unit      |

| SCL clock frequency          | Fscl   |                  | -   | -   | 400        | kHz       |

| SCL minimum high pulse width | Twscкн |                  | 10  | -   | -          | μs        |

| SCL minimum low pulse width  | TWSCKL |                  | 10  | -   | -          | μs        |

| Start condition hold time    | TDSTAH | Load capacitance | 5   | -   | -          | μS        |

| Start condition setup time   | TDSTAS | CL=20pF          | 5   | -   | -          | μS        |

| Stop condition setup time    | TDSTOS |                  | 5   | -   | -          | μS        |

| SDA output hold time         | TDSOH  |                  | 5   | -   | -          | μS        |

| SCL output delay time        | TDSOS  |                  | 5   | -   | -          | μS        |

| SDA input setup time         | TDSIS  |                  | 80  | -   | -          | ns        |

| SDA input hold time          | TDSIH  |                  | 0   | -   | -          | ns        |

Note: SCL clock frequency is fixed to 400kHz

#### Start condition (SDA falling edge while SCL=1), Stop condition (SDA rising edge while SCL=1)

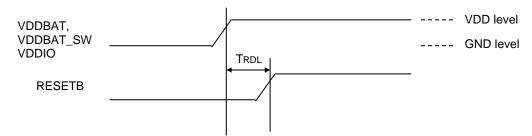

#### Reset operation

#### (Ta = -20 to +75 deg.C)

| Item                                           | Symbol | Condition                                             | Min | Тур | Max | Unit |

|------------------------------------------------|--------|-------------------------------------------------------|-----|-----|-----|------|

| RESETB propagation<br>delay time<br>(Power on) | Trdl   | Start supplying power<br>(VDDBAT,VDDBAT_SW,<br>VDDIO) | 20  | -   | -   | ms   |

| RESETB Pulse width                             | TRPLS  | RESETB pin                                            | 1   | -   | -   | μS   |

Power on reset function

Reset function from RESETB pin

It is possible to reset internal circuit by asserting RESETB after power supply is on.

It is possible to reset internal circuit by same way even if it is not power sequence. Internal circuit will move to normal state after oscillation circuit become stable by clock stabilizing circuit after reset function.

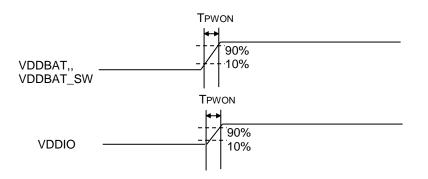

#### • Power on

(Ta = -20 to +75 deg.C)

| Item                                                        | Symbol   | Condition                                                | Min | Тур | Max | Unit |

|-------------------------------------------------------------|----------|----------------------------------------------------------|-----|-----|-----|------|

| VDD pin rising time                                         | Tpwon    | While power on<br>VDD pins (VDDBAT,<br>VDDBAT_SW,VDDIO)  |     | 1   | 5   | ms   |

| Time difference between<br>VDD pin while power<br>on state  | TPWONdly | While power on<br>VDD pins (VDDBAT,<br>VDDBAT_SW,VDDIO)  | 0   | -   | -   | ms   |

| Time difference between<br>VDD pin while power<br>off state | TPWOFdly | While power off<br>VDD pins (VDDBAT,<br>VDDBAT_SW,VDDIO) | 0   | -   | -   | ms   |

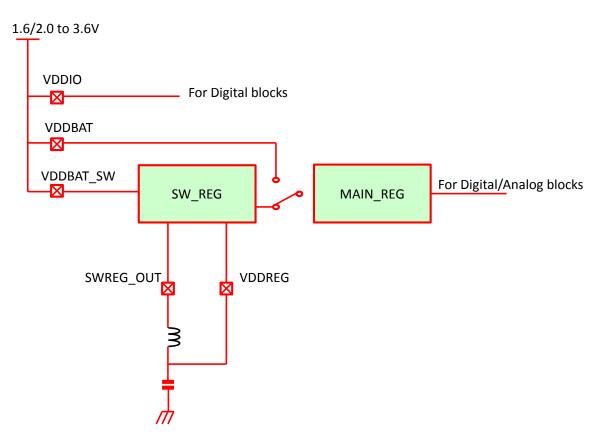

## Power Supply system and Operating status

Overview: ML7125-00X integrate 3 regulators which are Linear Regulator (here in after MAIN\_REG) providing power supply to MAIN logiv block, RF block, Switching Regulator (here in after SW\_REG) and Low Power Regulator (here in after LP\_REG) mainly used during power saving mode. Choice of regulator gives efficient low power saving mode depending on operating status.

• Power Supply domain

Figure below shows block diagram by power supply domain in ML7125-00X. Those blocks indicated by "Partial Power Shutdown" will be stop supplying power during power saving mode so called Deep Sleep Mode.

## • Internal Regulator

ML7125-00X has internal regulator which are Linear Regulator (MAIN\_Reg) and Switching Regulator(SW\_REG). Figure shown below depict internal regulator blocks and related pins.

#### ML7125-001/ML7125-002

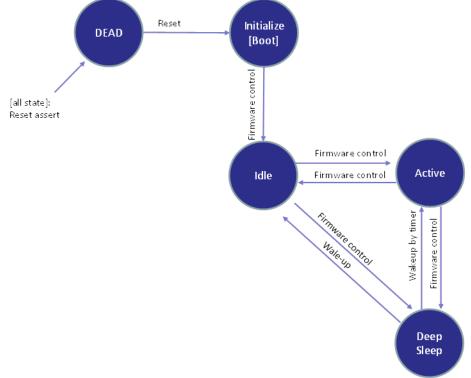

### • POWER MODE

ML7125-00X has Power mode shown below. Each state and these state transitions are explained in following section.

#### Fig.1 Power state transition and operating mode

#### [DEAD]

Assert hardware reset after start supplying power. ML7125-00X will move to Initialize/Boot state after power on reset event.

#### [Initialize/Boot]

ML7125-00X will start boot process after hardware reset. Boot program will initialize peripheral blocks nd start loading parameters. When Boot process completed, it will move to Idle state byfirmware control.

#### [Idle]

Idle state is the state that inernal MCU is available to process. User application can be execute in this state. Hence power supply for RF block will be suspended. Systtem clock 26MHz will be supplied while in Idle state.

#### [Active]

Active state is the state that RF communication shall be performed. In this state, most of blocks such as RF block, internal MCU, 26MHz clock oscillator are available to use. Peripheral block may be configured to stop clock supplying in order to save redundant power consumption.

#### [Deep Sleep]

Deep Sleep mode is power saving mode when the chip is in between connection event or application is not used for certain amount of time. Transition to Deep Sleep Mode is controlled by firmware. In Deep Sleep Mode, power supply to part of blocks are suspended in order to reduce standby current consumption. (Deep Sleep with Shutdown) Deep Sleep Mode uses 32.768kHz clock only, recovery to other state is initiated by Wake Up timer or Wakeup Factor condition.

#### Wakeup Factor

Wakeup Factor is necessary to return from Deep sleep mode or Application Sleep. Wakeup Factor, low state of GPIO1 pin or WAKEUP pin, will be detected, and RF block clock will start to oscillate.

#### • Operating Status

Table shown below indicate operating status of internal clock by power mode. LP\_REG and MAIN\_REG is powered all the time. Enable and Disable control will be done for MAIN\_REG.

| Block                      |         |                   | Power Mode |            |            |

|----------------------------|---------|-------------------|------------|------------|------------|

| DIOCK                      | DEAD    | Initialize [Boot] | ldle       | Active     | Deep Sleep |

| LP_REG                     | DISABLE | ENABLE            | ENABLE     | ENABLE     | ENABLE     |

| MAIN_REG /<br>SW_REG       | DISABLE | ENABLE            | ENABLE     | ENABLE     | DISABLE    |

| хо                         | DISABLE | ENABLE            | SELECTABLE | ON         | OFF        |

| LPCLK                      | DISABLE | SELECTABLE        | SELECTABLE | SELECTABLE | SELECTABLE |

| RF                         | DISABLE | ON                | OFF        | ON         | OFF        |

| IO CELLS                   | OFF     | ON                | ON         | ON         | ON         |

| LP_TIMER,<br>LP_LOGIC etc. | OFF     | ON                | ON         | ON         | ON         |

| SRAM 8kB                   | OFF     | ON                | ON         | ON         | ON         |

| SRAM 20kB                  | OFF     | ON/OFF            | ON/OFF     | ON/OFF     | ON/OFF     |

| Mask ROM 96kB              | OFF     | ON                | ON         | ON         | OFF        |

| MAIN_LOGIC                 | OFF     | ON                | ON         | ON         | OFF        |

ENABLE:ENABLE while POWER is ON DISABLE:DISABLE while POWER is ON ON: POWER is ON OFF: POWER is OFF ON/OFF: Available to select ON or OFF SELECTABLE:Available to select ENABLE or DISABLE

## Operating Mode

ML7125-00X support 3 operating modes, outline of each operating mode and supported product is shown in table shown below.

| Operating mode      |                 | Outline                                                                                                                                                                                      | ML7125-001    | ML7125-002    |

|---------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|

| BACI mode           |                 | Lapis original application interface mode,<br>it require HOST MCU externally. SPI is<br>used in order to exchange<br>command/event between ML7125-00X<br>and Host MCU.                       | Supported     | Not Supported |

| HCI mode            |                 | Bluetooth standard compatible mode,<br>UART interface is used in order to<br>exchange command/event between<br>ML7125-00X and Host MCU.                                                      | Supported     | Supported     |

|                     | Standalone type | Application mode donwload its program<br>code into internal SRAM. Standalone type<br>of application perform without external<br>Host MCU.                                                    | Not supported | Supported     |

| APPLICATION<br>mode | Add-on type     | Application mode download its profram<br>code into internal SRAM. Add-on type of<br>application provide command base control<br>and data transmission based on Lapis<br>original AT-command. | Not supported | Supported     |

ML7125-00X will choose operating mode while it is boot process, the choice will be made depending on pin condition shown below. Additionally in Application mode, it is decided to move appropriate operating mode depending on contents of configuration parameter which is read during boot process. It is not possible to transit one mode to another while ML7125-00X is working. Reset process has to be made if mode change is required.

| Operating Mode |                 | Operating Mode Pin condition of ML7125-001 of boot sequence |                       | Pin condition of ML7125-002 during<br>boot sequence |         |

|----------------|-----------------|-------------------------------------------------------------|-----------------------|-----------------------------------------------------|---------|

|                |                 | UART_RXD                                                    | GPIO3<br>(PS_CONTROL) | UART_RXD                                            | GPIO3   |

| BACI Mode      |                 | Low                                                         | Х                     | Not supported                                       |         |

| HCI Mode       |                 | High                                                        | Х                     | High                                                | Pull-Up |

| APPLICATION    | Standalone type | Not su                                                      | oported               | Low/High                                            | Low     |

| Mode           | Add-on type     | Not su                                                      | oported               | High                                                | Low     |

Low:Low input High:High input Pull-Up:Pull-Up to VDDHV X:OPEN(output)

Details of each Operating Modes are shown in following sections.

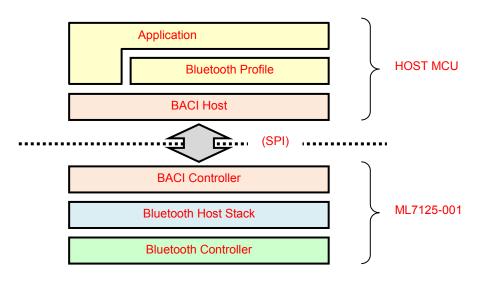

## BACI Mode

Protocol stack structure when ML7125-00X is in BACI mode is shown below. ML7125-00X will communicate with HOST-CPU by SPI interface or UART interface. Lapis original API called Bluetooth Application Controller Interface (BACI) will be used in order to exchange messages (command, event and data)

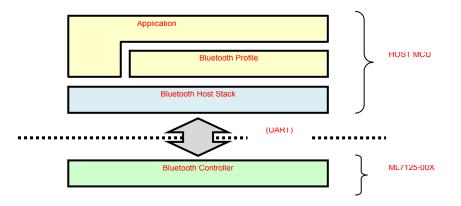

## HCI Mode

Protocol stack structure when ML7125-00X is in HCI mode is shown below.

ML7125-00X will communicate with HOST-CPU by UART interface. HCI command, event defined by Bluetooth Core Specification is available to use. Vendor specific HCI command is defined in our user's application.

Note: ML7125-002 will start up by HCI mode if UART interface is connected and configuration parameter indicates Add-on mode is disabled. Power saving control using WAKEUP signal is available to use.

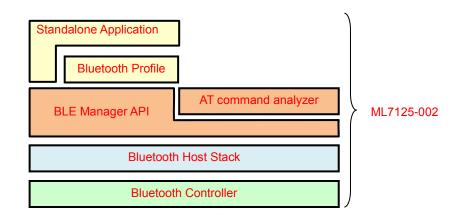

#### • Application Mode – Standalone type

When EEPROM is attached and configuration parameter is indicated, ML7125-002 will work as Application mode. With this Mode, Firmware stored in CODE\_RAM area in EEPROM will be downloaded and executed after boot process. In this type of application mode, HOST MCU is not mandatory required. This type of application code is assuming to collect data from sensor devices and transmit to other device through Bluetooth radio.

Protocol stack structure when ML7125-002 is in Application mode – Standalone type is shown below.

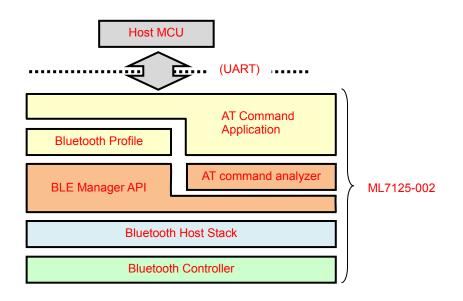

#### • Application Mode – Add-on type

When EEPROM is attached and configuration parameter is indicated, ML7125-002 will work as Application mode. With this Mode, Firmware stored in CODE\_RAM area in EEPROM will be downloaded and executed after boot process. Add-on type of application mode is assuming to use with HOST MCU using simple command and data interface defined by Lapis. It is possible to work Protocol stack structure when ML7125-002 is in Application mode – Standalone type is shown below.

## Functional features

## • Bluetooth<sup>®</sup> feature

ML7125-00X is Bluetooth<sup>®</sup> Core Specification v4.1 compatible, it is supporting Low Energy Feature. Following table and figure shows part of Link layer features supported by ML7125-00X.

| Product name | core spec<br>version | Supported role  | number of connectable device(s) | Number of connectable device(s) |

|--------------|----------------------|-----------------|---------------------------------|---------------------------------|

| ML7125-001   | v4.1                 | Master or Slave | 2 devices                       | 2 devices                       |

| ML7125-002   | v4.1                 | Slave only      | 1 device                        | 1 device                        |

#### • SPI interface description

Possible combination of parameters are described below when SPI-SLAVE block are used as HOST interface.

| Table 1 SPI_SLAVE Settings |                                 |  |  |

|----------------------------|---------------------------------|--|--|

| Parameter                  | Spec                            |  |  |

| Bit rate                   | Typ. 32.768KHz<br>Max. 1.625MHz |  |  |

| SPI mode                   | Motorola SPI (Mode 3)           |  |  |

| Data size                  | 8 bits                          |  |  |

| Chip select                | Low Active                      |  |  |

Possible selection of SLAVE MODE, MULTI SLAVE or SINGLE SLAVE. Sequences is shown below.

#### MULTI SLAVE

SINGLE SLAVE

#### • UART interface description

Possible combination of parameters are described below when UART block are used as HOST interface.

| Table 2 UART Settings |            |  |

|-----------------------|------------|--|

| Parameter             | Spec       |  |

| Baud rate             | 57600bps   |  |

| Data size             | 8 bits     |  |

| Parity bit            | No parity  |  |

| Stop bit              | 1 stop bit |  |

| Flow control          | No         |  |

## • I2C Interface description

Parameters related to I2C interface are shown below.

| Table 3 I2C Settings |               |  |  |

|----------------------|---------------|--|--|

| Parameter            | Configuration |  |  |

| Master/Slave         | Master        |  |  |

| Data rate            | 400KHz/220kHz |  |  |

| Address bit          | 7 bit         |  |  |

| Data bit             | 8 bit         |  |  |

| Protocol             | None          |  |  |

## • LPCLK description

LPCLK (from external or oscillator) is used while ML7125 is in deep sleep mode in order to reduce power consumption. It is possible to choose either 32.768kHz or 16.384kHz

| Table 4 LPCLK Settings |                                      |  |  |

|------------------------|--------------------------------------|--|--|

| Parameter              | Configuration                        |  |  |

| Frequency              | 32.768KHz or 16.384KHz               |  |  |

| Duty                   | None (32.768KHz),<br>50% (16.384KHz) |  |  |

## Package dimensions

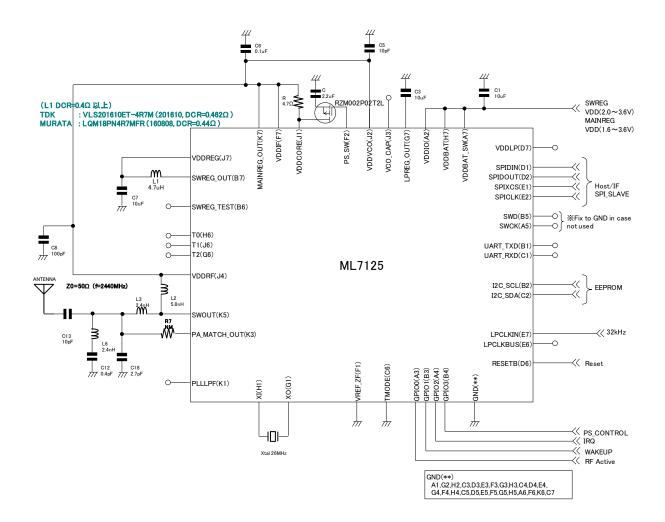

## Application example

The following circuit shows the typical application circuit. This circuit shows ML7125-00X Application example and does not guarantee the characteristics. It is recommended that choosing and finalizes the best component value by evaluation on the target board.

## Revision History

| Degument        |                    | Pa                  | age                |                                                                                |

|-----------------|--------------------|---------------------|--------------------|--------------------------------------------------------------------------------|

| Document<br>No. | Date               | Previous<br>Edition | Current<br>Edition | Description                                                                    |

| FEDL712501      | November, 30, 2015 | _                   | _                  | 1 <sup>st</sup> Edition                                                        |

| FEDL712502      | December,10,2015   | 1                   | 1                  | Current Consumptions condition added                                           |

|                 |                    | -                   | 2                  | Support Function List added                                                    |

|                 |                    | 2                   | 2                  | Block Diagram modified                                                         |

|                 |                    | 6                   | 6                  | PS_SW pin description changes                                                  |

|                 |                    | 7                   | 7                  | Unused pins<br>SPIDOUT/TM2 definition changes<br>SWD/SWCK definitionadded      |

|                 |                    | 14                  | 14                 | Delete GPADC Characteristic                                                    |

|                 |                    | 16                  | 16                 | SPI interface description modified                                             |

|                 |                    | 28                  | 28                 | SPI Sequences added                                                            |

| FEDL7125-03     | January,26,2016    | 24                  | 24                 | Pin condition of ML7125-002 during boot<br>sequence modified<br>Footnote added |

| FEDL7125-04     | April,5,2016       | 1                   | 1                  | Featire condition modified                                                     |

|                 |                    | 2                   | 2                  | Block Diagram modified                                                         |

|                 |                    | 3                   | 3                  | PIN ASSIGNMENT<br>SPIDIN/SPIDOUT/SPICLK/SPIXCS PIN<br>ASSIGNMENT modified      |

|                 |                    | 4                   | 4                  | LPXO renamed LPCLK                                                             |

|                 |                    | 6                   | 6                  | FUCNTION modified<br>MAIN Regulator→Linear Regulator                           |

|                 |                    | 8                   | 8                  | VDDBAT_SW added in Condition                                                   |

|                 |                    | 9                   | 9                  |                                                                                |

|                 |                    | 19                  | 19                 |                                                                                |

|                 |                    | 9                   | 9                  | Master Clock Condition modified                                                |

|                 |                    | 11                  | 11                 | H level Voltage Output Condition<br>modified                                   |

|                 |                    | 12                  | 12                 | TX power Condition modified                                                    |

|                 |                    | 20                  | 20                 | LPXO in figure renamed LPCLK                                                   |

|                 |                    | 21                  | 21                 | Change pin name SWREG_FB to<br>VDDREG in Internal Regulator figure.            |

|                 |                    | 29                  | 29                 | LPCLK description modified                                                     |

| <br> |    |                                                            |

|------|----|------------------------------------------------------------|

| 31   | 31 | Change pin name SWREG_FB to VDDREG in Application Example. |

## **NOTES**

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.