**Gate Driver Providing Galvanic Isolation Series**

# Isolation voltage 2500Vrms 1ch Gate Driver Providing Galvanic Isolation

# BM60054AFV-C

# **General Description**

The BM60054AFV-C is a gate driver with isolation voltage 2500Vrms, I/O delay time of 120ns, and a minimum input pulse width of 90ns. Fault signal output function, ready signal output function, under voltage lockout (UVLO) function, thermal protection function, short current protection (SCP) function, miller clamp function and switching controller function, output state feedback function are all built-in.

# **Key Specifications**

Isolation Voltage: 2500Vrms

Maximum Gate Drive Voltage: 20V (Max)

I/O Delay Time: 120ns (Max)

Minimum Input Pulse Width: 90ns (Max)

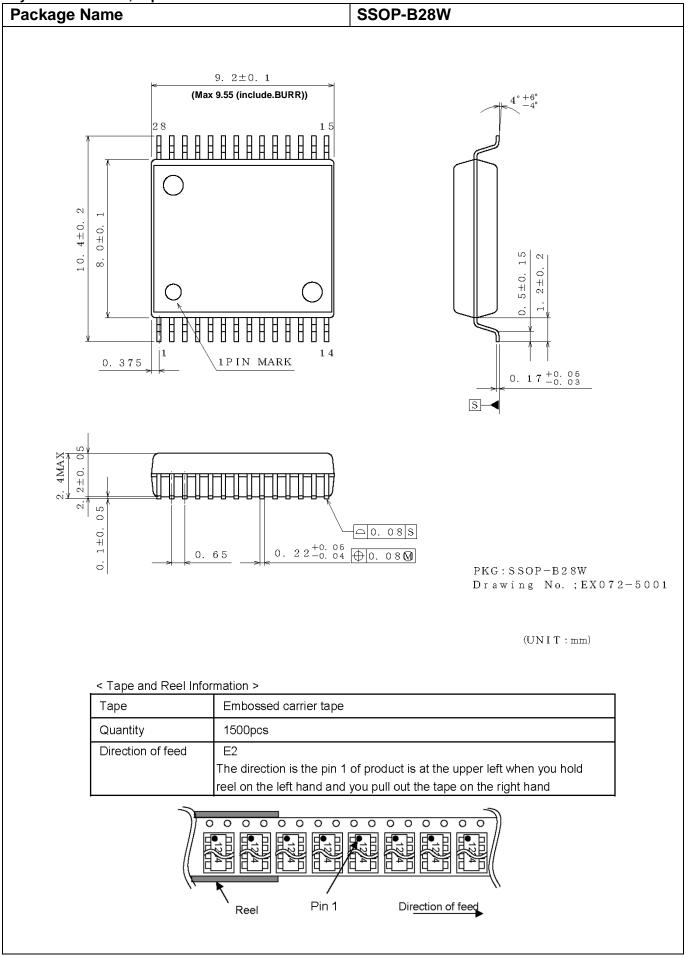

Package W(Typ) x D(Typ) x H(Max) SSOP-B28W 9.2 mm x 10.4 mm x 2.4 mm

# **Features**

- AEC-Q100 Qualified<sup>(Note 1)</sup>

- Fault Signal Output Function

- Ready Signal Output Function

- Under Voltage Lockout Function

- Short Circuit Protection Function

- Soft Turn-Off Function for Short Circuit Protection (Adjustable Turn-Off time)

- Thermal Protection Function

- Active Miller Clamping

- Switching Controller Function

- Output State Feedback Function

- UL1577 Recognized: File No. E356010

(Note 1) Grade 1

# **Applications**

- Automotive Inverter

- Automotive DC-DC Converter

- Industrial inverter System

- UPS System

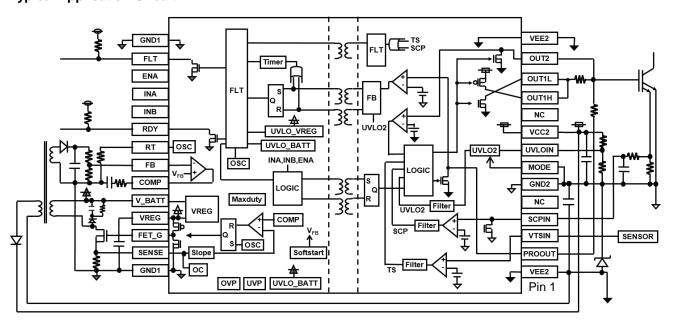

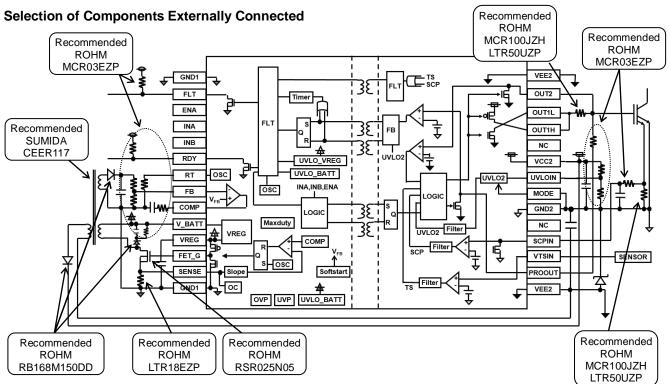

# **Typical Application Circuit**

Figure 1. Typical Application Circuit

# Contents

| General Description                                                                                     | 1  |

|---------------------------------------------------------------------------------------------------------|----|

| Features                                                                                                |    |

| Applications                                                                                            |    |

| Key Specifications                                                                                      |    |

| Package                                                                                                 |    |

| Typical Application Circuit                                                                             | 1  |

| Contents                                                                                                |    |

| Recommended Range of External Constants                                                                 | 3  |

| Pin Configuration                                                                                       | 3  |

| Pin Descriptions                                                                                        |    |

| Description of Functions and Examples of Constant Setting                                               | 6  |

| Absolute Maximum Ratings                                                                                | 17 |

| Thermal Resistance                                                                                      | 18 |

| Recommended Operating Conditions                                                                        | 18 |

| Insulation Related Characteristics                                                                      | 18 |

| Electrical Characteristics                                                                              |    |

| UL1577 Ratings Table                                                                                    | 21 |

| Typical Performance Curves                                                                              | 22 |

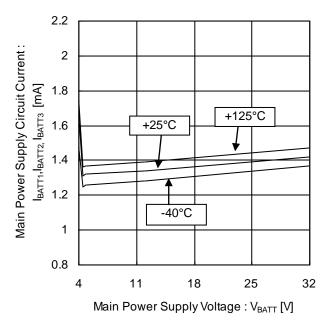

| Figure 19. Main Power Supply Circuit Current vs Main Power Supply Voltage                               | 22 |

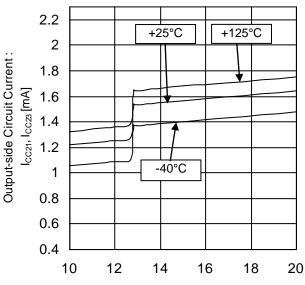

| Figure 20. Output-side Circuit Current vs Output-side Positive Supply Voltage (MODE=H, VEE2=0V, OUT1=L) | 22 |

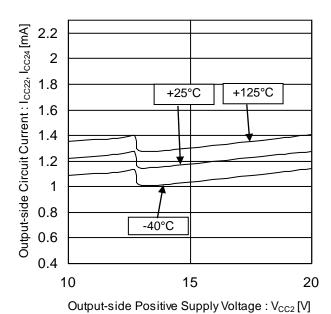

| Figure 21. Output-side Circuit Current vs Output-side Positive Supply Voltage (MODE=H, VEE2=0V, OUT1=H) | 22 |

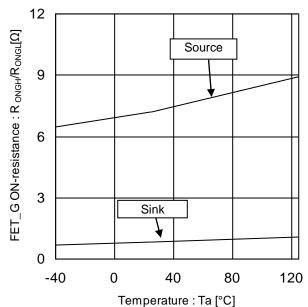

| Figure 22. FET_G ON-resistance vs Temperature (Source /Sink)                                            |    |

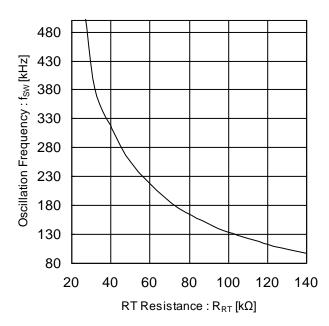

| Figure 23. Oscillation Frequency vs RT Resistance                                                       |    |

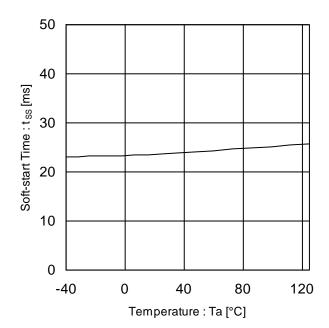

| Figure 24. Soft-start Time vs Temperature                                                               |    |

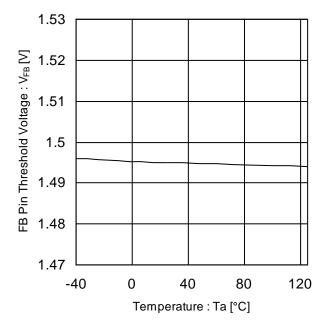

| Figure 25. FB Pin Threshold Voltage vs Temperature                                                      |    |

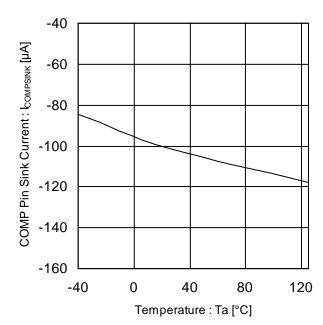

| Figure 26. COMP Pin Sink Current vs Temperature                                                         |    |

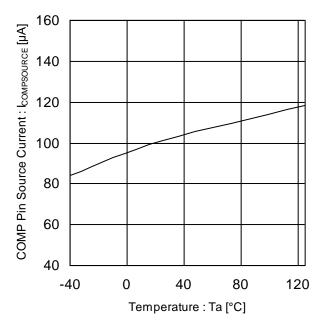

| Figure 27. COMP Pin Source Current vs Temperature                                                       |    |

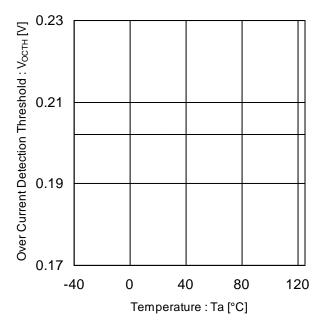

| Figure 28. Over Current Detection Threshold vs Temperature                                              |    |

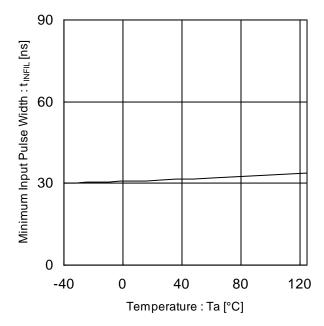

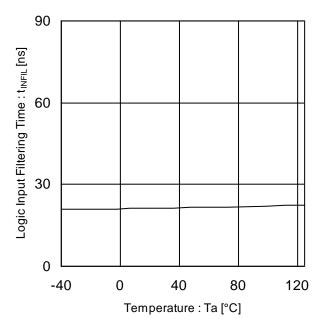

| Figure 29. Logic Input Filtering Time vs Temperature (L pulse)                                          |    |

| Figure 30. Logic Input Filtering Time vs Temperature (H pulse)                                          |    |

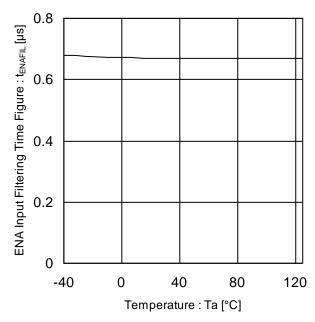

| Figure 31. ENA Input Filtering Time Figure vs Temperature                                               |    |

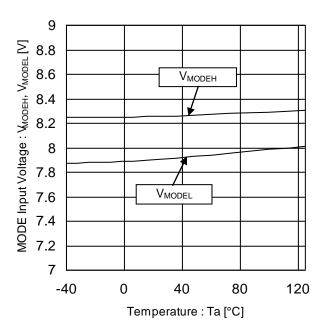

| Figure 32. MODE Input Voltage vs Temperature (V <sub>CC2</sub> =14V)                                    |    |

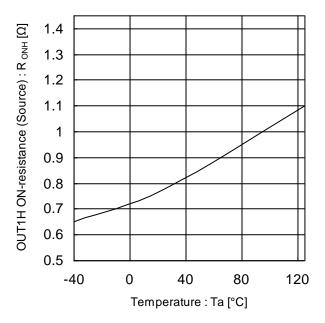

| Figure 33. OUT1H ON-resistance (Source) vs Temperature (I <sub>OUT1H</sub> =-40mA)                      |    |

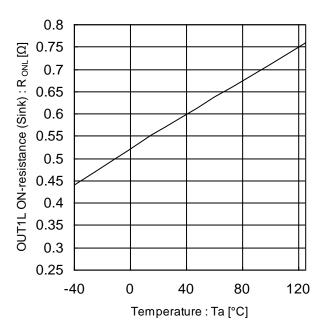

| Figure 34. OUT1L ON-resistance (Sink) vs Temperature (I <sub>OUT1L</sub> =40mA)                         |    |

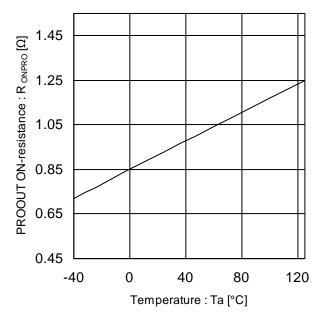

| Figure 35. PROOUT ON-resistance vs Temperature (I <sub>PROOUT</sub> =40mA)                              |    |

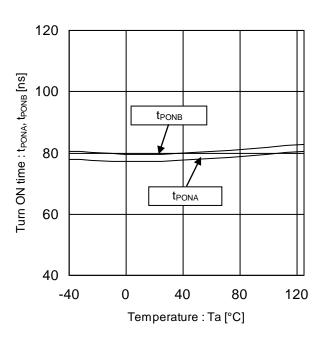

| Figure 36. Turn ON time vs Temperature                                                                  |    |

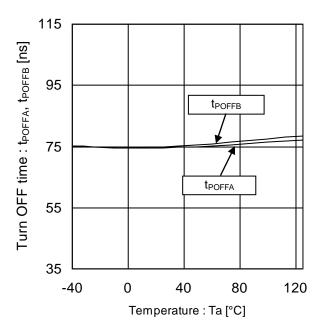

| Figure 37. Turn OFF time vs Temperature                                                                 |    |

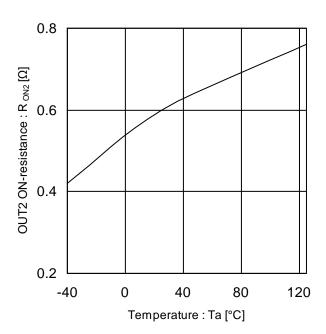

| Figure 38. OUT2 ON-resistance vs Temperature (I <sub>OUT2</sub> =40mA)                                  |    |

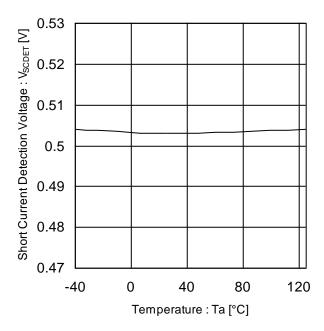

| Figure 39. Short Current Detection Voltage vs Temperature                                               |    |

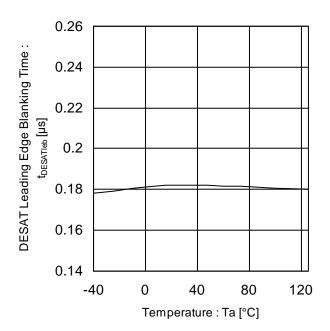

| Figure 40. DESAT Leading Edge Blanking Time vs Temperature                                              |    |

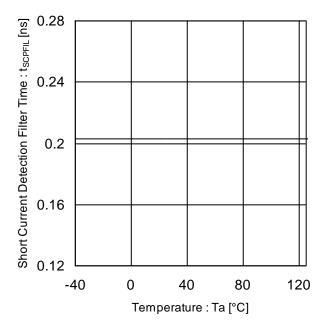

| Figure 41. Short Current Detection Filter Time vs Temperature                                           |    |

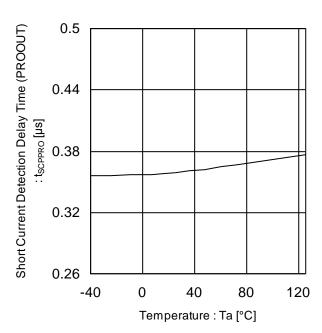

| Figure 42. Short Current Detection Delay Time (PROOUT) vs Temperature                                   |    |

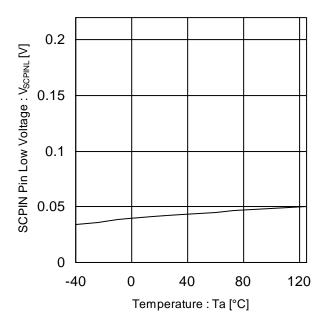

| Figure 43. SCPIN Pin Low Voltage vs Temperature                                                         |    |

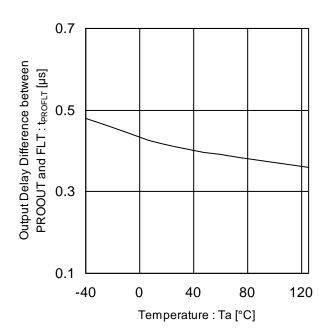

| Figure 44. Output Delay Difference between PROOUT and FLT vs Temperature                                | 28 |

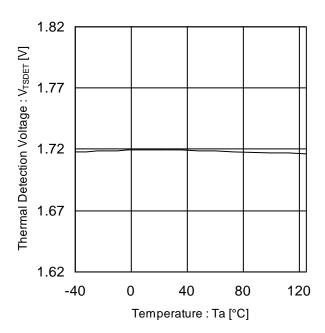

| Figure 45. Thermal Detection Voltage vs Temperature                                                     |    |

| Selection of Components Externally Connected                                                            |    |

| I/O Equivalence Circuits                                                                                |    |

| Operational Notes                                                                                       |    |

| Ordering Information                                                                                    |    |

| Marking Diagram                                                                                         |    |

| Physical Dimension, Tape and Reel Information                                                           |    |

| Revision History                                                                                        | 38 |

# **Recommended Range of External Constants**

| Pin Name    | Cymbol            | Recor | Unit |      |       |

|-------------|-------------------|-------|------|------|-------|

| FILLINALLIE | Symbol            | Min   | Тур  | Max  | Offic |

| VREG        | $C_{VREG}$        | 1.0   | 3.3  | 10.0 | μF    |

| VCC2        | C <sub>VCC2</sub> | 0.33  | -    | -    | μF    |

| RT          | R <sub>RT</sub>   | 24    | 68   | 150  | kΩ    |

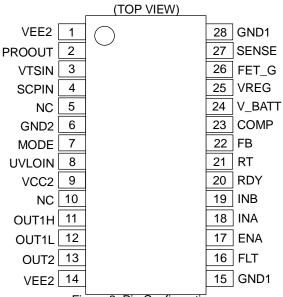

# **Pin Configuration**

Figure 2. Pin Configuration

# **Pin Descriptions**

| Pin No. | Pin Name | Function                                                     |

|---------|----------|--------------------------------------------------------------|

| 1       | VEE2     | Output-side negative power supply pin                        |

| 2       | PROOUT   | Soft turn-off pin/Gate voltage input pin                     |

| 3       | VTSIN    | Temperature sensor voltage input pin                         |

| 4       | SCPIN    | Short circuit current detection pin                          |

| 5       | NC       | Non-connection                                               |

| 6       | GND2     | Output-side ground pin                                       |

| 7       | MODE     | Mode selection pin of output-side UVLO                       |

| 8       | UVLOIN   | Output-side UVLO setting input pin                           |

| 9       | VCC2     | Output-side positive power supply pin                        |

| 10      | NC       | Non-connection                                               |

| 11      | OUT1H    | Source side output pin                                       |

| 12      | OUT1L    | Sink side output pin                                         |

| 13      | OUT2     | Miller Clamp pin                                             |

| 14      | VEE2     | Output-side negative power supply pin                        |

| 15      | GND1     | Input-side ground pin                                        |

| 16      | FLT      | Fault output pin                                             |

| 17      | ENA      | Input enabling signal input pin                              |

| 18      | INA      | Control input pin A                                          |

| 19      | INB      | Control input pin B                                          |

| 20      | RDY      | Ready output pin                                             |

| 21      | RT       | Switching frequency setting pin for switching controller     |

| 22      | FB       | Error amplifier inverting input pin for switching controller |

| 23      | COMP     | Error amplifier output pin for switching controller          |

| 24      | V_BATT   | Main power supply pin                                        |

| 25      | VREG     | Input-side internal power supply pin                         |

| 26      | FET_G    | MOS FET control pin for switching controller                 |

| 27      | SENSE    | Current detection pin for switching controller               |

| 28      | GND1     | Input-side ground pin                                        |

|         |          |                                                              |

# Pin Descriptions - continued

1. V\_BATT (Main power supply pin)

This is the main power supply pin. Connect a bypass capacitor between V\_BATT and GND1 in order to suppress voltage variations.

# 2. GND1 (Input-side ground pin)

The GND1 pin is a ground pin on the input side.

### 3. VCC2 (Output-side positive power supply pin)

The VCC2 pin is a positive power supply pin on the output side. To reduce voltage fluctuations due to OUT1H/L pin output current and due to the driving current of the internal transformers, connect a bypass capacitor between VCC2 and GND2 pins.

# 4. VEE2 (Output-side negative power supply pin)

The VEE2 pin is a negative power supply pin on the output side. To suppress voltage fluctuations due to OUT1H/L pin output current and due to the driving current of the internal transformers, connect a bypass capacitor between the VEE2 and the GND2 pins. Connect the VEE2 pin to the GND2 pin when no negative power supply is used.

### 5. GND2 (Output-side ground pin)

The GND2 pin is a ground pin on the output side. Connect the GND2 pin to the emitter/source of a power device.

### 6. INA, INB, ENA (Control Input pin)

The INA, INB, ENA are pins used to determine output logic.

| ENA | INB | INA | OUT1H | OUT1L |

|-----|-----|-----|-------|-------|

| L   | X   | X   | Hi-Z  | L     |

| Н   | Н   | X   | Hi-Z  | L     |

| Н   | L   | L   | Hi-Z  | L     |

| Н   | L   | Н   | Н     | Hi-Z  |

# 7. FLT (Fault output pin)

The FLT pin is an open drain pin used to output a fault signal when short circuit protection function (SCP) or thermal protection function is activated, and fault state (FLT=L output) is released in rising of ENA (L to H).

| Status                                      | FLT  |

|---------------------------------------------|------|

| While in normal operation                   | Hi-Z |

| When SCP or thermal protection is activated | L    |

# 8. RDY (Ready output pin)

The RDY pin is an open drain pin that outputs an internal abnormal state (V\_BATT UVLO, VCC2 UVLO, output state feedback). 'output state feedback' is a function to compare gate logic monitored by the PROOUT pin with input logic, and outputs L when it does not match.

| Status                                                        | RDY  |

|---------------------------------------------------------------|------|

| While in normal operation                                     | Hi-Z |

| V_BATT UVLO or VCC2 UVLO or Output state feedback (disaccord) | L    |

# 9. MODE (Mode selection pin of output-side UVLO)

The MODE pin is a pin which selects internal threshold or external setting threshold for output-side UVLO.

| MODE      | Output-side UVLO threshold voltage                             |

|-----------|----------------------------------------------------------------|

| L (=GND2) | Setting by external (Use UVLOIN pin)                           |

| H (=VCC2) | Fixed (=V <sub>UVLO2L</sub> ) (Connect UVLOIN pin to VCC2 pin) |

# 10. UVLOIN (Output-side UVLO setting input pin)

The UVLOIN pin is a pin for deciding UVLO setting value of VCC2. The threshold value of UVLO can be set by dividing the resistance voltage of VCC2. UVLOIN activates only at MODE pin=L. When MODE pin=H, connect UVLOIN pin to VCC2 pin.

### 11. OUT1H, OUT1L (Output pin)

The OUT1H pin is a source side pin used to drive the gate of a power device, and the OUT1L pin is a sink side pin used to drive the gate of a power device.

# Pin Descriptions - continued

12. OUT2 (Miller Clamp pin)

This is the miller clamp pin for preventing a rise of gate voltage due to miller current of output element connected to OUT1H/L. It also functions as a pin for monitoring gate voltage for miller clamp. OUT2 pin voltage become less than  $V_{\text{OUT2ON}}$  (typ 2.0V), miller clamp function operates. OUT2 should be connect to VEE2 when miller clamp function is not used.

13. PROOUT (Soft turn-off pin/Gate voltage input pin)

This is a pin for soft turn-off of output pin when short circuit protection or thermal protection is in action. It also functions as a pin for monitoring gate voltage for output state feedback function.

14. SCPIN (Short circuit current detection pin)

The SCPIN pin is a pin used to detect current for short circuit protection. When the SCPIN pin voltage exceeds  $V_{\text{SCDET}}$ , SCP function will be activated. This may cause the IC to malfunction in an open state. To avoid such trouble, short circuit the SCPIN pin to the GND2 pin when the short circuit protection is not used. In order to prevent the wrong detection due to noise, the noise filter time  $t_{\text{SCPFIL}}$  is set.

15. VTSIN (Temperature sensor voltage input pin)

The VTSIN pin is a temperature sensor voltage input pin, which can be used for thermal protection of an output device. If VTSIN pin voltage becomes  $V_{TSDET}$  or less, the thermal protection function will be activated. IC may malfunction in the open status, so be sure to supply the VTSIN more than  $V_{TSDET}$  if the thermal protection function is not used. In order to prevent the wrong detection due to noise, the noise mask time  $t_{TSFIL}$  is set. In addition, it can be used also as compulsive shutdown pin other than a temperature sense by inputting a comparator output etc.

16. RT (Switching frequency setting pin for switching controller)

The RT pin is a pin used to make setting of switching frequency of switching controller. The switching frequency is determined by the resistance value connected between RT and GND1. The value of switching frequency is determined by the value of the resistor  $R_{\rm RT}$ .

$$F_{SW} = 1/(7.3 \times 10^{-8} \times R_{RT} + 2.2 \times 10^{-4})$$

[kHz]

17. FB (Error amplifier inverting input pin for switching controller)

This is a voltage feedback pin of the switching controller. This pin combine with voltage monitoring at overvoltage protection function and under voltage protection function for switching controller. When overvoltage or under voltage protection is activated, switching controller will be at OFF state (FET\_G pin outputs low). When the protection holding time t<sub>DCDCRLS</sub> is completed, the protection function will be released. Under voltage function is not activated during soft-start.

18. COMP (Error amplifier output pin for switching controller)

This is the gain control pin of the switching controller. Connect a phase compensation capacitor and resistor.

19. VREG (Input-side internal power supply pin)

This is the input-side internal power supply pin. Be sure to connect a capacitor between VREG and GND1 even when the switching controller is not used, in order to prevent oscillation and suppress voltage variation due to FET\_G output current and IC internal transformer drive current.

20. FET\_G (MOS FET control pin for switching controller)

This is a MOSFET control pin for the switching controller transformer drive.

21. SENSE (Current detection pin for switching controller)

This is a pin connected to the resistor of the switching controller current feedback. This pin combines with current monitoring at overcurrent restriction function for switching controller. When overcurrent restriction is activated, switching controller will be at OFF state (FET\_G pin outputs Low), and the overcurrent restriction function will be released in the next switching period.

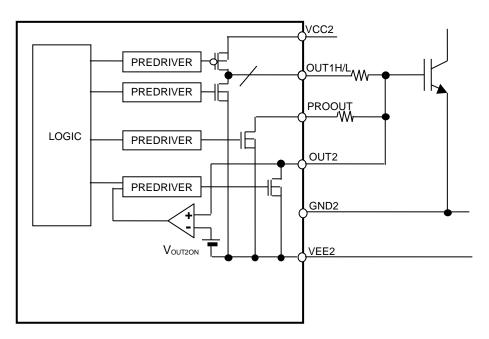

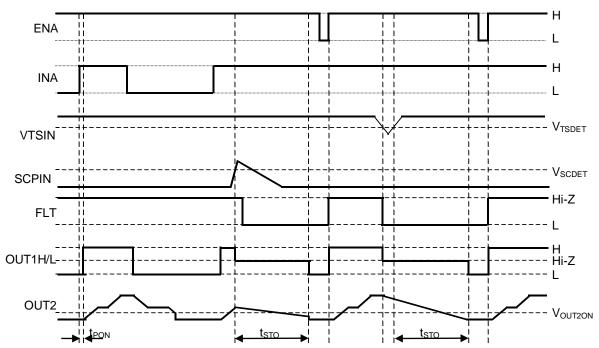

1. Miller Clamp Function

When OUT1H/L=Hi-Z/L and OUT2 pin voltage<V<sub>OUT2ON</sub>, internal MOS of OUT2 pin is turned ON and miller clamp function operates. Miller clamp will be maintained until next turn on (OUT1H/L=H/Hi-Z).

During short circuit protection and thermal protection, the miller clamp function does not operate and the miller clamp function is enabled after soft turn-off release time  $t_{STO}$  has passed.

| IN | OUT2 pin input voltage        | OUT2 output |

|----|-------------------------------|-------------|

| L  | less than V <sub>OUT2ON</sub> | L           |

| Н  | X                             | Hi-Z        |

Figure 3. Block Diagram of Miller Clamp Function

Figure 4. Timing Chart of Miller Clamp Function

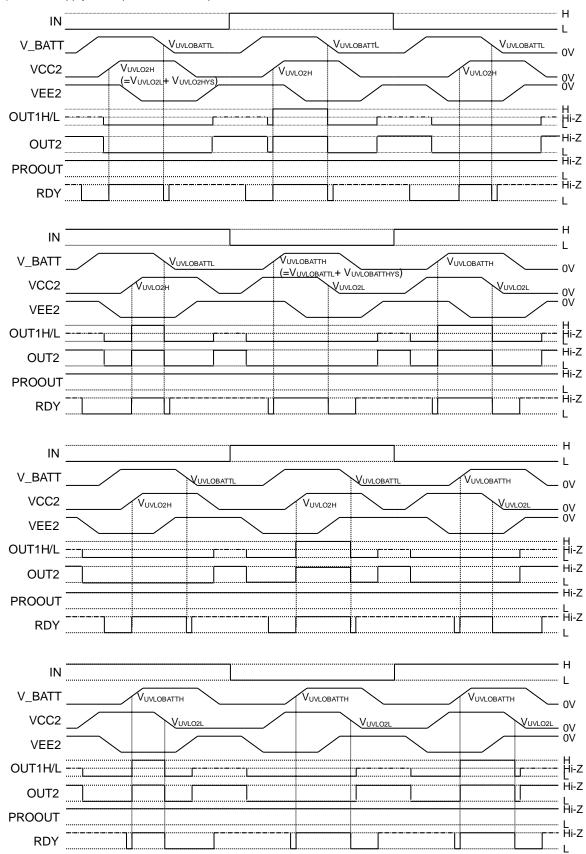

2. Under Voltage Lockout (UVLO)Function

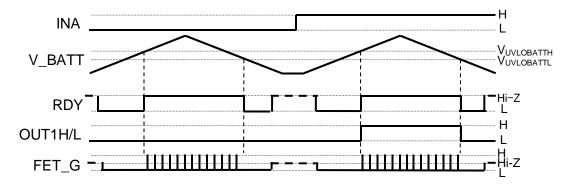

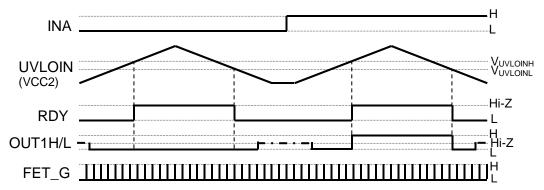

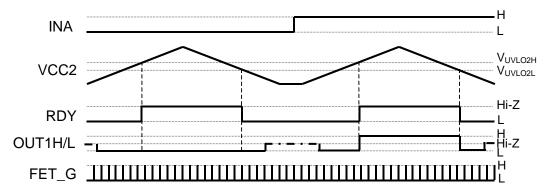

The BM60054AFV-C incorporates the under voltage lockout (UVLO) function on V\_BATT and VCC2. When the power supply voltage drops to  $V_{UVLOBATTL}$ ,  $V_{UVLOINL}$  (MODE=L), or  $V_{UVLO2L}$  (MODE=H), the OUT1H/L pin will output the "Hi-Z/L" and the RDY pin will output the "L" signal. When the power supply voltage rises to  $V_{UVLOBATTH}$  (= $V_{UVLOBATTL}$ + $V_{UVLOBATTL}$ + $V_{UVLOINH}$ + $V_{UVLOBATTH}$ 1, and to prevent miss-triggers due to noise, mask time  $V_{UVLOBATTH}$ 1, and  $V_{UVLO2H}$ 1, are set on both voltage sides.

Figure 5. V\_BATT UVLO Function Operation Timing Chart

Figure 6. VCC2 UVLO Function Operation Timing Chart (MODE=L)

Figure 7. VCC2 UVLO Function Operation Timing Chart (MODE=H)

- - - : Since the V\_BATT to GND1 pin voltage is low and the output MOS does not turn ON, the output pins become Hi-Z conditions.

- · - · : Since the VCC2 to VEE2 pin voltage is low and the output MOS does not turn ON, the output pins become Hi-Z conditions.

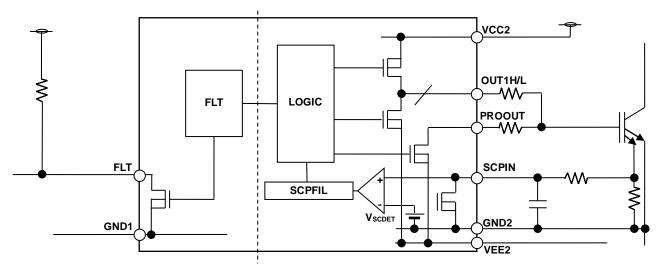

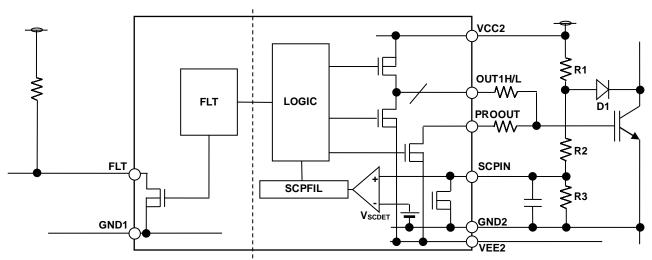

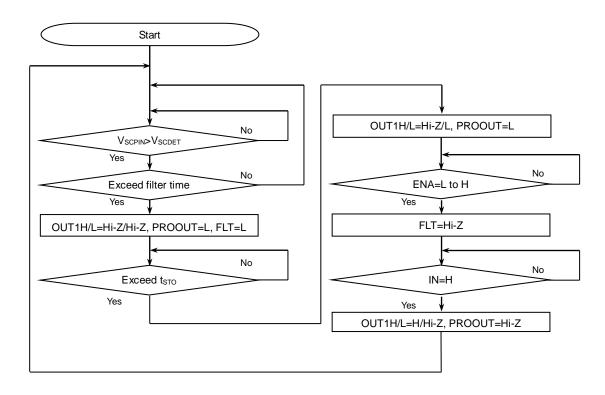

3. Short Circuit Protection Function (SCP, DESAT)

When the SCPIN pin voltage exceeds  $V_{SCDET}$ , the SCP function will be activated. When the SCP function is activated, the OUT1H/L pin voltage will be set to the "Hi-Z/Hi-Z" level and the PROOUT pin voltage will go to the "L" level first (soft turn-off). Next, after  $t_{STO}$  has passed, OUT1H/L pin become Hi-Z/L (PROOUT pin hold L). When the rising edge is put in the ENA pin after ENA=L (> $t_{ENAFIL}$ ), the SCP function will be released. When OUT1H/L=Hi-Z/L or Hi-Z/Hi-Z, MOSFET is built-in between SCPIN pin and GND2 pin turns ON to discharge  $C_{BLANK}$  for desaturation protection function. When OUT1H/L=H/Hi-Z, internal MOSFET connected to SCPIN pin turns OFF. Collector/drain voltage  $V_{DESAT}$  at which desaturation protection function operates and blank time  $t_{BLANKouternal}$  can be set by the following formula.

$$\begin{split} V_{DESAT} &= V_{SCDET} \times \frac{R3 + R2}{R3} - V_{F_{D1}} & \text{[V]} \\ V_{CC2_{MIN}} &> V_{SCDET} \times \frac{R3 + R2 + R1}{R3} & \text{[V]} \\ t_{BLANKoutemal} &= -\frac{R2 + R1}{R3 + R2 + R1} \times R3 \times C_{BLANK} \times \ln(1 - \frac{R3 + R2 + R1}{R3} \times \frac{V_{SCDET}}{V_{CC2}}) + t_{DESATleb} & \text{[s]} \end{split}$$

| W                  |       | 設定参考値 |       |

|--------------------|-------|-------|-------|

| V <sub>DESAT</sub> | R1    | R2    | R3    |

| 4.0V               | 15 kΩ | 39kΩ  | 4.7kΩ |

| 4.5V               | 15 kΩ | 47kΩ  | 5.1kΩ |

| 5.0V               | 15 kΩ | 51kΩ  | 5.1kΩ |

| 5.5V               | 15 kΩ | 27kΩ  | 2.4kΩ |

| 6.0V               | 15 kΩ | 33kΩ  | 2.7kΩ |

| 6.5V               | 15 kΩ | 62kΩ  | 4.7kΩ |

| 7.0V               | 15 kΩ | 47kΩ  | 3.3kΩ |

| 7.5V               | 15 kΩ | 20kΩ  | 1.3kΩ |

| 8.0V               | 15 kΩ | 82kΩ  | 5.1kΩ |

| 8.5V               | 15 kΩ | 62kΩ  | 3.6kΩ |

| 9.0V               | 15 kΩ | 33kΩ  | 1.8kΩ |

| 9.5V               | 15 kΩ | 75kΩ  | 3.9kΩ |

| 10.0V              | 15 kΩ | 68kΩ  | 3.3kΩ |

Figure 8. Block Diagram of Short Circuit Protection

Figure 9. Block Diagram of DESAT

Figure 10. SCP Operation Timing Chart

Figure 11. SCP Operation Status Transition Diagram

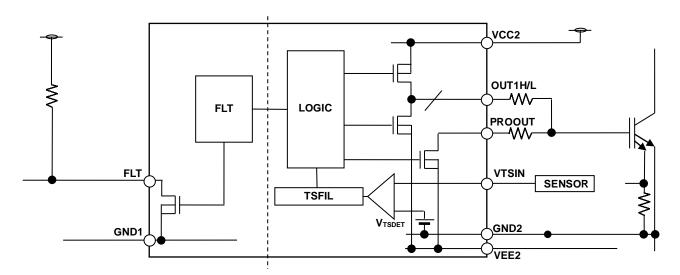

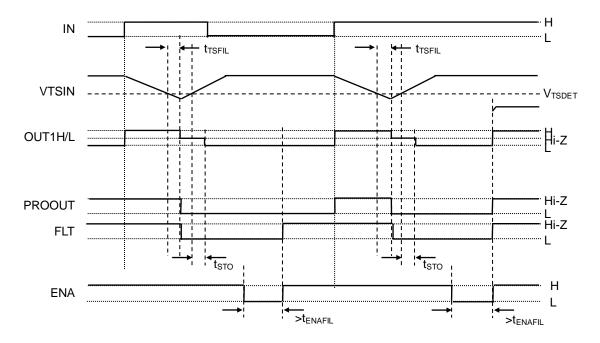

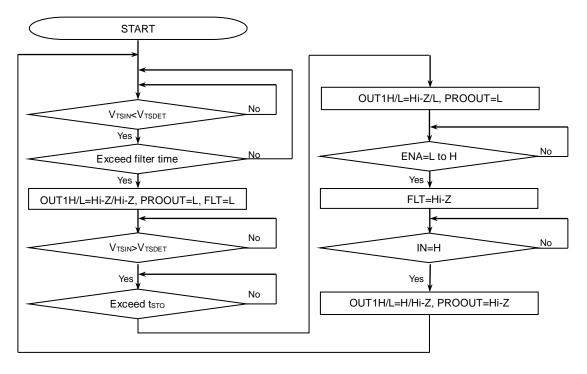

4. Thermal Protection Function

When the VTSIN pin voltage becomes  $V_{TSDET}$  or less, the thermal protection function will be activated. When the thermal protection function is activated, the OUT1H/L pin voltage will be set to the "Hi-Z/Hi-Z" level and the PROOUT pin voltage will go to the "L" level first (soft turn-off). Next, when the VTSIN pin voltage rises to the threshold value and after  $t_{STO}$  has passed, OUT1H/L pin become Hi-Z/L (PROOUT pin hold L).

When the rising edge is put in the ENA pin after ENA=L (>t<sub>ENAFIL</sub>), the thermal protection function will be released.

Figure 12. Block Diagram of thermal protection function

Figure 13. Thermal Protection Function Operation Timing Chart

Figure 14. Thermal Protection Function Operation Status Transition Diagram

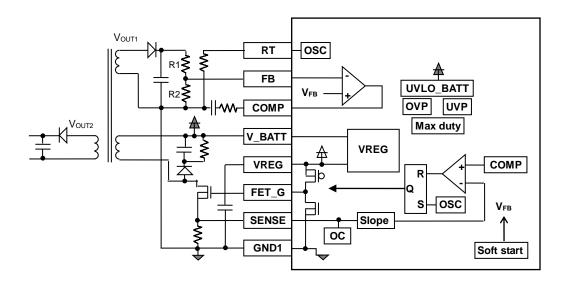

# 5. Switching Controller

### (a) Basic action

This IC has a built-in switching power supply controller which repeats ON/OFF synchronizing with internal clock set by RT pin. When  $V_BATT$  voltage is supplied ( $V_{BATT} > V_{UVLOBATTH}$  (= $V_{UVLOBATTL} + V_{UVLOBATTHYS}$ )), FET\_G pin starts switching by soft-start. Output voltage is determined by the following equation by external resistance and winding ratio "n" of fly back transformer (n= $V_{OUT2}$  side winding number/ $V_{OUT1}$  side winding number)

$$V_{OUT2} = V_{FB} \times \{ (R_1 + R_2) / R_2 \} \times n$$

[V]

# (b) Max duty

When, for example, output load is large, and voltage level of SENSE pin does not reach current detection level, output is forcibly turned OFF by Maximum ON Duty (D<sub>ONMAX</sub>).

# (c) Protection function

The switching controller has protection function as overvoltage protection (OVP), and under voltage protection (UVP) monitoring the voltage of FB pin.

When the protection function is activated, switching controller will be OFF state (FET\_G pin outputs Low). The protection holding time (t<sub>DCDCRLS</sub>) is completed, the protection function will be released. Under voltage function is not activated during soft-start.

Figure 15. Block Diagram of switching controller

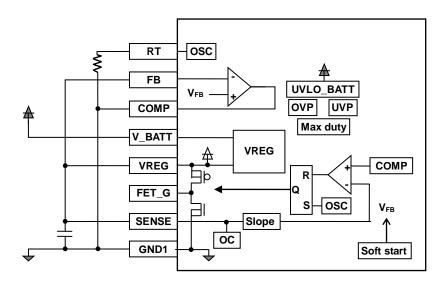

(d) The pin handling when not using switching controller

When not using switching controller, do pin handling as follows.

| Pin no. | Pin name | Processing method         |

|---------|----------|---------------------------|

| 21      | RT       | pull down in GND1 by 68kΩ |

| 22      | FB       | connect to VREG           |

| 23      | COMP     | connect to GND1           |

| 24      | V_BATT   | connect power supply      |

| 25      | VREG     | connect capacitor         |

| 26      | FET_G    | open                      |

| 27      | SENSE    | connect to VREG           |

Figure 16. The pin handling when not using switching controller

# 6. Gate State Monitoring Function

When input logic and gate logic of output device monitored with PROOUT pin are compared, a logic L is output from RDY pin when they disaccord. In order to prevent the detection error due to delay of input and output, OSFB filter time tosebell is provided.

# Description of Functions and Examples of Constant Setting – continued (7) I/O Condition Table

| ,,,,,, | John Table       |        | Input |       |       |     |     |     |      | Output |       |       |      |        |      |      |

|--------|------------------|--------|-------|-------|-------|-----|-----|-----|------|--------|-------|-------|------|--------|------|------|

| No.    | Status           | V_BATT | VCC2  | SCPIN | VTSIN | ENA | INB | INA | OUT2 | PROOUT | ОПТ1Н | OUT1L | OUT2 | PROOUT | FLT  | RDY  |

| 1      | SCP              | 0      | 0     | Н     | Н     | Н   | L   | Н   | Н    | Х      | Hi-Z  | Hi-Z  | Hi-Z | L      | L    | Hi-Z |

| 2      | 304              | 0      | 0     | Н     | Н     | Η   | L   | Η   | L    | Χ      | Hi-Z  | Hi-Z  | L    | L      | L    | Hi-Z |

| 3      | UVLO_VBATT       | UVLO   | 0     | L     | Ι     | Χ   | Χ   | Χ   | Ι    | Ι      | Hi-Z  | ш     | Hi-Z | Hi-Z   | Hi-Z | L    |

| 4      | OVLO_VBATT       | UVLO   | 0     | L     | Н     | Χ   | Χ   | Χ   | L    | L      | Hi-Z  | L     | L    | Hi-Z   | Hi-Z | L    |

| 5      | UVLO_VCC2        | 0      | UVLO  | L     | Н     | Χ   | Χ   | Χ   | Ι    | Ι      | Hi-Z  | L     | Hi-Z | Hi-Z   | Hi-Z | L    |

| 6      | UVLO_VCC2        | 0      | UVLO  | L     | Н     | Χ   | Χ   | Χ   | L    | L      | Hi-Z  | L     | L    | Hi-Z   | Hi-Z | L    |

| 7      | Thermal          | 0      | 0     | L     | L     | Χ   | Χ   | Χ   | Н    | Χ      | Hi-Z  | Hi-Z  | Hi-Z | L      | L    | Hi-Z |

| 8      | protection       | 0      | 0     | L     | L     | Χ   | Χ   | Χ   | L    | Х      | Hi-Z  | Hi-Z  | Hi-Z | L      | L    | Hi-Z |

| 9      | Diaghla          | 0      | 0     | L     | Н     | L   | Χ   | Χ   | Н    | Н      | Hi-Z  | L     | Hi-Z | Hi-Z   | Hi-Z | L    |

| 10     | Disable          | 0      | 0     | L     | Н     | L   | Χ   | Χ   | L    | L      | Hi-Z  | L     | L    | Hi-Z   | Hi-Z | Hi-Z |

| 11     | INB active       | 0      | 0     | L     | Н     | Н   | Н   | Χ   | Н    | Н      | Hi-Z  | L     | Hi-Z | Hi-Z   | Hi-Z | L    |

| 12     | IND active       | 0      | 0     | L     | Н     | Н   | Н   | Χ   | L    | L      | Hi-Z  | L     | L    | Hi-Z   | Hi-Z | Hi-Z |

| 13     | Normal Operation | 0      | 0     | L     | Н     | Н   | L   | L   | Н    | Н      | Hi-Z  | L     | Hi-Z | Hi-Z   | Hi-Z | L    |

| 14     | 1 1              | 0      | 0     | L     | Н     | Н   | L   | L   | L    | L      | Hi-Z  | L     | L    | Hi-Z   | Hi-Z | Hi-Z |

| 15     | Normal Operation | 0      | 0     | L     | Н     | Н   | L   | Н   | Н    | Н      | Н     | Hi-Z  | Hi-Z | Hi-Z   | Hi-Z | Hi-Z |

| 16     | H Input          | 0      | 0     | L     | Н     | Н   | L   | Н   | L    | L      | Н     | Hi-Z  | Hi-Z | Hi-Z   | Hi-Z | L    |

○ : > UVLO, X:Don't care

(8) Power Supply Startup/Shutdown Sequence

: Since the VCC2 to VEE2 pin voltage is low and the output MOS does not turn ON, the output pins become Hi-Z conditions.

----: Since the V\_BATT to GND1 pin voltage is low and the RDY output MOS does not turn ON, the output pins become Hi-Z conditions.

Figure 17. Power Supply Startup/Shutdown Sequence

# **Absolute Maximum Ratings**

| Parameter                                                             | Symbol                 | Limit                                                       | Unit |

|-----------------------------------------------------------------------|------------------------|-------------------------------------------------------------|------|

| Main Power Supply Voltage                                             | $V_{BATT}$             | -0.3 to +40.0 <sup>(Note 2)</sup>                           | V    |

| Output-side Positive Supply Voltage                                   | V <sub>CC2</sub>       | -0.3 to +24.0 <sup>(Note 3)</sup>                           | V    |

| Output-side Negative Supply Voltage                                   | V <sub>EE2</sub>       | -15.0 to +0.3 <sup>(Note 3)</sup>                           | V    |

| Maximum Difference Between Output-Side Positive and Negative Voltages | V <sub>MAX2</sub>      | 30.0                                                        | V    |

| INA, INB, ENA Pin Input Voltage                                       | V <sub>IN</sub>        | -0.3 to +7.0 <sup>(Note 2)</sup>                            | V    |

| MODE Pin Input Voltage                                                | $V_{MODE}$             | -0.3 to + $V_{CC2}$ +0.3 or +24.0 <sup>(Note 3)</sup>       | V    |

| SCPIN Pin Input Voltage                                               | V <sub>SCPIN</sub>     | -0.3 to +V <sub>CC2</sub> +0.3 or +24.0 <sup>(Note 3)</sup> | V    |

| VTSIN Pin Input Voltage                                               | V <sub>VTS</sub>       | -0.3 to +V <sub>CC2</sub> +0.3 or +24.0 <sup>(Note 3)</sup> | V    |

| UVLOIN Pin Input Voltage                                              | V <sub>UVLOIN</sub>    | -0.3 to +V <sub>CC2</sub> +0.3 or +24.0 <sup>(Note 3)</sup> | V    |

| OUT1H, OUT1L Pin Output Current (Peak 10µs)                           | I <sub>OUT1PEAK</sub>  | 5.0 <sup>(Note 4)</sup>                                     | Α    |

| OUT2 Pin Output Current (Peak 10µs)                                   | I <sub>OUT2PEAK</sub>  | 5.0 <sup>(Note 4)</sup>                                     | Α    |

| PROOUT Pin Output Current (Peak 10µs)                                 | I <sub>PROOUTPEA</sub> | 2.5 <sup>(Note 4)</sup>                                     | Α    |

| FLT, RDY Pin Output Current                                           | I <sub>FLT</sub>       | 10                                                          | mA   |

| FET_G Pin Output Current (Peak 1µs)                                   | I <sub>FET_GPEAK</sub> | 1                                                           | А    |

| Storage Temperature Range                                             | Tstg                   | -55 to +150                                                 | °C   |

| Junction Temperature                                                  | Tjmax                  | +150                                                        | °C   |

Caution 1: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

caution 2: Should by any chance the maximum ratings.

Caution 2: Should by any chance the maximum junction temperature rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, design a PCB boards with thermal resistance taken into consideration by increasing board size and copper area so as not to exceed the maximum junction temperature rating.

(Note 2) Relative to GND1

(Note 3) Relative to GND2

(Note 4) Should not exceed Tjmax=150°C

# Thermal Resistance<sup>(Note 5)</sup>

| Dorometer                                                      | Cumbal        | Thermal Res            | Linit                    |      |

|----------------------------------------------------------------|---------------|------------------------|--------------------------|------|

| Parameter                                                      | Symbol        | 1s <sup>(Note 7)</sup> | 2s2p <sup>(Note 8)</sup> | Unit |

| SSOP-B28W                                                      |               |                        |                          |      |

| Junction to Ambient                                            | $\theta_{JA}$ | 112.9                  | 64.4                     | °C/W |

| Junction to Top Characterization Parameter <sup>(Note 6)</sup> | $\Psi_{JT}$   | 34                     | 23                       | °C/W |

(Note 5) Based on JESD51-2A (Still-Air).

(Note 6) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 7) Using a PCB board based on JESD51-3.

| (INOLE I) | osing a | I CD | Dualu | Daseu | OHUL   | JDJ 1-J. |

|-----------|---------|------|-------|-------|--------|----------|

| (Note 8)  | Using a | PCB  | board | based | on JES | SD51-7.  |

| (Note 8) Using a PCB board based     | on JESD51-7. |                    |           |                 |           |

|--------------------------------------|--------------|--------------------|-----------|-----------------|-----------|

| Layer Number of<br>Measurement Board | Material     | Board Size         |           |                 |           |

| Single                               | FR-4         | 114.3mm x 76.2mm x | k 1.57mmt |                 |           |

| Тор                                  |              |                    |           |                 |           |

| Copper Pattern                       | Thickness    |                    |           |                 |           |

| Footprints and Traces                | 70μm         |                    |           |                 |           |

| Layer Number of<br>Measurement Board | Material     | Board Size         |           |                 |           |

| 4 Layers                             | FR-4         | 114.3mm x 76.2mm   | x 1.6mmt  |                 |           |

| Тор                                  |              | 2 Internal Layers  |           | Bottom          |           |

| Copper Pattern                       | Thickness    | Copper Pattern     | Thickness | Copper Pattern  | Thickness |

| Footprints and Traces                | 70µm         | 74.2mm x 74.2mm    | 35µm      | 74.2mm x 74.2mm | 70µm      |

# **Recommended Operating Conditions**

| Parameter                                                             | Symbol            | Min | Тур | Max  | Unit |

|-----------------------------------------------------------------------|-------------------|-----|-----|------|------|

| Main Power Supply Voltage <sup>(Note 9)</sup>                         | V <sub>BATT</sub> | 4   | 12  | 32   | V    |

| Output-side Positive Supply Voltage <sup>(Note 10)</sup>              | V <sub>CC2</sub>  | 10  | 15  | 20   | V    |

| Output-side Negative Supply Voltage <sup>(Note 10)</sup>              | V <sub>EE2</sub>  | -12 | -   | 0    | V    |

| Maximum Difference Between Output-Side Positive and Negative Voltages | V <sub>MAX2</sub> | 10  | -   | 28   | V    |

| Switching Frequency for Switching Controller                          | f <sub>SWR</sub>  | 100 | -   | 500  | kHz  |

| Operating Temperature Range                                           | Topr              | -40 | +25 | +125 | °C   |

(Note 9) Relative to GND1 (Note 10) Relative to GND2

# **Insulation Related Characteristics**

| Parameter                                     | Symbol           | Characteristic   | Unit |

|-----------------------------------------------|------------------|------------------|------|

| Insulation Resistance (V <sub>IO</sub> =500V) | Rs               | >10 <sup>9</sup> | Ω    |

| Insulation Withstand Voltage/1min             | V <sub>ISO</sub> | 2500             | Vrms |

| Insulation Test Voltage/1sec                  | V <sub>ISO</sub> | 3000             | Vrms |

# **Electrical Characteristics**

(Unless otherwise specified Ta=-40°C to +125°C, V<sub>BATT</sub>=4V to 32V, V<sub>CC2</sub>=UVLO to 20V, V<sub>FF2</sub>=-12V to 0V)

| Unless otherwise specified Ta=-40°C  |                          |                      |            |                      |         |                                               |

|--------------------------------------|--------------------------|----------------------|------------|----------------------|---------|-----------------------------------------------|

| Parameter                            | Symbol                   | Min                  | Тур        | Max                  | Unit    | Conditions                                    |

| General                              | I                        |                      |            |                      |         | 1                                             |

| Main Power Supply                    | I <sub>BATT1</sub>       | 1.0                  | 1.6        | 2.2                  | mA      | V <sub>BATT</sub> =4V                         |

| Circuit Current 1                    | ·BAIII                   |                      |            |                      |         | · DATT                                        |

| Main Power Supply                    | I <sub>BATT2</sub>       | 0.7                  | 1.3        | 1.9                  | mA      | V <sub>BATT</sub> =12V                        |

| Circuit Current 2                    | IBATTZ                   | <b></b>              |            |                      | 1117 \  | V BATT- 12 V                                  |

| Main Power Supply                    | I <sub>BATT3</sub>       | 0.8                  | 1.4        | 2.0                  | mA      | V <sub>BATT</sub> =32V                        |

| Circuit Current 3                    | 'BATT3                   | 0.0                  | 1          | 2.0                  | ША      | ABALL-OZ A                                    |

| Output-side Circuit Current 1        | I <sub>CC21</sub>        | 0.8                  | 1.5        | 2.2                  | mA      | V <sub>CC2</sub> =14V, OUT1=L                 |

| Output-side Circuit Current 2        | I <sub>CC22</sub>        | 0.4                  | 1.1        | 1.8                  | mΑ      | V <sub>CC2</sub> =14V, OUT1=H                 |

| Output-side Circuit Current 3        | I <sub>CC23</sub>        | 0.9                  | 1.6        | 2.3                  | mΑ      | V <sub>CC2</sub> =18V, OUT1=L                 |

| Output-side Circuit Current 4        | I <sub>CC24</sub>        | 0.5                  | 1.2        | 1.9                  | mA      | V <sub>CC2</sub> =18V, OUT1=H                 |

|                                      | _                        | 4.0                  | 4.6        | 0.4                  |         | V <sub>CC2</sub> =16V, V <sub>EE2</sub> =-8V, |

| Output-side Circuit Current 5        | I <sub>CC25</sub>        | 1.0                  | 1.6        | 2.4                  | mA      | OUT1=L                                        |

|                                      | _                        |                      |            |                      |         | V <sub>CC2</sub> =16V, V <sub>EE2</sub> =-8V, |

| Output-side Circuit Current 6        | I <sub>CC26</sub>        | 0.6                  | 1.3        | 2.0                  | mA      | OUT1=H                                        |

| Switching Power Supply Control       | er                       |                      | L          |                      |         | 1                                             |

|                                      |                          |                      |            |                      |         | 4.2V <v<sub>BATT≤32V</v<sub>                  |

| FET_G Output Voltage H1              | $V_{FETGH1}$             | 3.8                  | 4.0        | 4.2                  | V       | I <sub>FET G</sub> =0A(open)                  |

|                                      |                          |                      |            |                      |         | V <sub>BATT</sub> ≤4.2V                       |

| FET_G Output Voltage H2              | $V_{FETGH2}$             | -                    | V_BATT-0.2 | V_BATT               | V       |                                               |

| FFT C Output Valtage I               |                          | 0                    |            | 0.0                  | 1/      | I <sub>FET_G</sub> =0A(open)                  |

| FET_G Output Voltage L               | V <sub>FETGL</sub>       | 0                    | -          | 0.3                  | V       | I <sub>FET_G</sub> =0A(open)                  |

| FET_G ON-resistance (Source)         | R <sub>ONGH</sub>        | 3                    | 6          | 12                   | Ω       | I <sub>FET_G</sub> =-10mA                     |

| FET_G ON-resistance (Sink)           | R <sub>ONGL</sub>        | 0.3                  | 0.6        | 1.3                  | Ω       | I <sub>FET_G</sub> =10mA                      |

| Oscillation Frequency                | f <sub>SW</sub>          | 182                  | 200        | 222                  | kHz     | RT=68kΩ                                       |

| Soft-start Time                      | t <sub>SS</sub>          | -                    | -          | 50                   | ms      |                                               |

| FB Pin Threshold Voltage             | V <sub>FB</sub>          | 1.47                 | 1.50       | 1.53                 | V       |                                               |

| FB Pin Input Current                 | I <sub>FB</sub>          | -0.8                 | 0          | +0.8                 | μΑ      |                                               |

| COMP Pin Sink Current                | I <sub>COMPSINK</sub>    | -160                 | -80        | -40                  | μΑ      |                                               |

| COMP Pin Source Current              | ICOMPSOURCE              | 40                   | 80         | 160                  | μΑ      |                                               |

| V_BATT UVLO ON Voltage               | V <sub>UVLOBATTL</sub>   | 3.20                 | 3.40       | 3.60                 | V       |                                               |

| V_BATT UVLO Hysteresis               | V <sub>UVLOBATTHYS</sub> | 0.07                 | 0.1        | 0.13                 | V       |                                               |

| V_BATT UVLO Filtering Time           | t <sub>UVLOBATTFIL</sub> | -                    | 2          | -                    | μs      |                                               |

| Maximum ON DUTY                      | D <sub>ONMAX</sub>       | -                    | 48         | -                    | %       |                                               |

| Over Voltage Detection Threshold     | V <sub>OVTH</sub>        | 1.60                 | 1.65       | 1.70                 | V       |                                               |

| Under Voltage Detection<br>Threshold | V <sub>UVTH</sub>        | 1.23                 | 1.30       | 1.37                 | V       |                                               |

| Over Current Detection Threshold     | V <sub>OCTH</sub>        | 0.17                 | 0.20       | 0.23                 | V       |                                               |

| Protection Holding Time              | t <sub>DCDCRLS</sub>     | 20                   | 40         | 60                   | ms      |                                               |

| Logic                                | -DODOKLO                 |                      |            |                      | 0       | ı                                             |

| Logic High Level Input Voltage       | V <sub>INH</sub>         | 2.0                  | -          | 5.5                  | V       | INA, INB, ENA                                 |

| Logic Low Level Input Voltage        | V <sub>INL</sub>         | 0                    | -          | 0.8                  | V       | INA, INB, ENA                                 |

| Logic Pull-Down Resistance           | R <sub>IND</sub>         | 25                   | 50         | 100                  | kΩ      | INA, INB, ENA                                 |

| Minimum Input Pulse Width            | t <sub>INFIL</sub>       | -                    | -          | 90                   | ns      | INA, INB                                      |

| ENA Input Filtering Time             | tenafil                  | _                    | 0.5        | 0.8                  | μs      | ENA                                           |

| MODE Low Level Input Voltage         | V <sub>MODEL</sub>       | 0                    | -          | 0.3xV <sub>CC2</sub> | μs<br>V | Relative to GND2                              |

| MODE High Level Input Voltage        |                          |                      | <u>-</u>   |                      | V       | Relative to GND2                              |

| MODE High Level Input voltage        | $V_{MODEH}$              | 0.7xV <sub>CC2</sub> | _          | $V_{CC2}$            | V       | INGIALIVE IO GINDZ                            |

# **Electrical Characteristics – continued**

(Unless otherwise specified Ta=-40°C to +125°C, VBATT=4V to 32V, VCC2=UVLO to 20V, VEE2=-12V to 0V)

| Unless otherwise specified 1a=-40°C                     |                                      | Min                  |                      |                      | Unit  |                                                       |

|---------------------------------------------------------|--------------------------------------|----------------------|----------------------|----------------------|-------|-------------------------------------------------------|

| Parameter                                               | Symbol                               | IVIII                | Тур                  | Max                  | Unit  | Conditions                                            |

| Output                                                  | Б                                    | 0.50                 | 0.05                 | 4.45                 | 0     | 1 – 40m A                                             |

| OUT1H ON-resistance (Source) OUT1L ON-resistance (Sink) | R <sub>ONH</sub><br>R <sub>ONL</sub> | 0.50<br>0.25         | 0.85<br>0.45         | 1.45<br>0.80         | Ω     | I <sub>OUT1H</sub> =-40mA<br>I <sub>OUT1L</sub> =40mA |

| ,                                                       |                                      |                      |                      |                      |       | V <sub>CC2</sub> =15V                                 |

| OUT1 Maximum Current                                    | I <sub>OUT1MAX</sub>                 | 3.0                  | 4.5                  | -                    | Α     | Guaranteed by design                                  |

| PROOUT ON-resistance                                    | R <sub>ONPRO</sub>                   | 0.45                 | 0.85                 | 1.55                 | Ω     | I <sub>PROOUT</sub> =40mA                             |

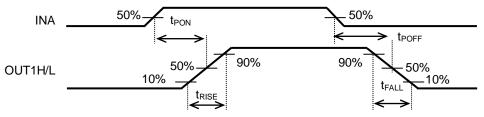

| Turn ON Time                                            | t <sub>PONA</sub>                    | 40                   | 80                   | 120                  | ns    | INA=PWM, INB=L                                        |

| rum en rume                                             | t <sub>PONB</sub>                    | 40                   | 80                   | 120                  | ns    | INA=H, INB=PWM                                        |

| Turn OFF Time                                           | t <sub>POFFA</sub>                   | 35                   | 75                   | 115                  | ns    | INA=PWM, INB=L                                        |

|                                                         | t <sub>POFFB</sub>                   | 35                   | 75                   | 115                  | ns    | INA=H, INB=PWM                                        |

| Propagation Distortion                                  | t <sub>PDISTA</sub>                  | -25                  | -5                   | +15                  | ns    | t <sub>POFFA</sub> — t <sub>PONA</sub>                |

| 1 Topagation Dictortion                                 | t <sub>PDISTB</sub>                  | -25                  | -5                   | +15                  | ns    | t <sub>POFFB</sub> — t <sub>PONB</sub>                |

| Rise Time                                               | t <sub>RISE</sub>                    | -                    | 50                   | -                    | ns    | 10nF between OUT1-VEE2                                |

| Fall Time                                               | t <sub>FALL</sub>                    | -                    | 50                   | -                    | ns    | Guaranteed by design                                  |

| OUT2 ON-resistance                                      | R <sub>ON2</sub>                     | 0.25                 | 0.45                 | 0.80                 | Ω     | I <sub>OUT2</sub> =40mA                               |

| OUT2 ON Threshold Voltage                               | V <sub>OUT2ON</sub>                  | 1.8                  | 2                    | 2.2                  | V     | Relative to V <sub>EE2</sub>                          |

| Common Mode Transient Immunity                          | CM                                   | 100                  | -                    | -                    | kV/μs | Guaranteed by design                                  |

| Protection Functions                                    |                                      |                      |                      | 1                    |       |                                                       |

| Output-side UVLO ON                                     | V <sub>UVLOINL</sub>                 | 0.85                 | 0.90                 | 0.95                 | V     | MODE=L                                                |

| Threshold Voltage (UVLOIN)                              | VUVLOINL                             | 0.65                 | 0.90                 | 0.95                 | V     | WODL-L                                                |

| Output-side UVLO Threshold                              | \/                                   | 0.10×                | 0.11×                | 0.12×                | V     | MODE=L                                                |

| Hysteresis (UVLOIN)                                     | Vuvloinhys                           | $V_{\text{UVLOINL}}$ | V <sub>UVLOINL</sub> | V <sub>UVLOINL</sub> | V     | WODE-E                                                |

| Output-side UVLO ON Voltage                             | $V_{UVLO2L}$                         | 10.9                 | 11.5                 | 12.1                 | V     | MODE=H                                                |

| Output-side UVLO Hysteresis                             | V <sub>UVLO2HYS</sub>                | 0.8                  | 1.2                  | 1.6                  | V     | MODE=H                                                |

| Output-side UVLO Filtering Time                         | t <sub>UVLO2FIL</sub>                | 6                    | 12                   | 22                   | μs    |                                                       |

| DESAT Leading Edge                                      | <b>t</b>                             | 0.14                 | 0.20                 | 0.26                 | 110   | Guaranteed by design                                  |

| Blanking Time                                           | t <sub>DESATIeb</sub>                | 0.14                 | 0.20                 | 0.26                 | μs    | Guaranteed by design                                  |

| Short Current Detection Voltage                         | V <sub>SCDET</sub>                   | 0.47                 | 0.50                 | 0.53                 | V     | Relative to GND2                                      |

| Short Current Detection Filtering Time                  | t <sub>SCPFIL</sub>                  | 0.12                 | 0.2                  | 0.28                 | μs    |                                                       |

| Short Current Detection                                 | t <sub>SCPPRO</sub>                  | 0.26                 | 0.38                 | 0.50                 | μs    |                                                       |

| Delay Time (PROOUT)                                     | ISCPPRO                              | 0.20                 | 0.50                 | 0.50                 | μδ    |                                                       |

| SCPIN Pin Low Voltage                                   | V <sub>SCPINL</sub>                  | -                    | 0.1                  | 0.22                 | V     | I <sub>SCPIN</sub> =1mA                               |

| Output Delay Difference                                 | t <sub>PROFLT</sub>                  | 0.1                  | 0.4                  | 0.7                  | μs    |                                                       |

| between PROOUT and FLT                                  | PROFLI                               | 0.1                  | 0.4                  | 0.7                  | μδ    |                                                       |

| Thermal Detection Voltage                               | V <sub>TSDET</sub>                   | 1.62                 | 1.72                 | 1.82                 | V     | Relative to GND2                                      |

| Thermal Detection Filtering Time                        | t <sub>TSFIL</sub>                   | 4                    | 10                   | 30                   | μs    |                                                       |

| Soft Turn Off Release Time                              | t <sub>STO</sub>                     | 30                   | -                    | 110                  | μs    |                                                       |

| FLT Output Low Voltage                                  | V <sub>FLTL</sub>                    | -                    | 0.18                 | 0.40                 | V     | I <sub>FLT</sub> =5mA                                 |

| Gate State H Detection                                  | V <sub>OSFBH</sub>                   | 4.5                  | 5.0                  | 5.5                  | V     | Relative to GND2                                      |

| Threshold Voltage                                       | V OSEBH                              | 4.0                  | 3.0                  | 5.5                  | v     | NGIQUYG IU GINDZ                                      |

| Gate State L Detection                                  | V <sub>OSFBL</sub>                   | 4.0                  | 4.5                  | 5.0                  | V     | Relative to GND2                                      |

| Threshold Voltage                                       | ▲ OSERF                              | ٦.٥                  | 7.0                  | 0.0                  | , v   | Noidilve to OND2                                      |

| OSFB Output Filtering Time                              | tosfbfil                             | 4.0                  | 6.2                  | 8.4                  | μs    |                                                       |

| RDY Output Low Voltage                                  | $V_{RDYL}$                           | -                    | 0.18                 | 0.40                 | V     | I <sub>RDY</sub> =5mA                                 |

Figure 18. INA to OUT1H/L Timing Chart

# **UL1577 Ratings Table**

Following values are described in UL Report.

| Parameter                               | Value | Unit | Conditions                                              |

|-----------------------------------------|-------|------|---------------------------------------------------------|

| Side 1 (Input Side) Circuit Current     | 1.3   | mA   | V <sub>BATT</sub> =12V, OUT1H/L=L                       |

| Side 2 (Output Side) Circuit Current    | 1.6   | mA   | V <sub>CC2</sub> =16V, V <sub>EE2</sub> =-8V, OUT1H/L=L |

| Side 1 (Input Side) Consumption Power   | 15.6  | mW   | V <sub>BATT</sub> =12V, OUT1H/L=L                       |

| Side 2 (Output Side) Consumption Power  | 38.4  | mW   | V <sub>CC2</sub> =16V, V <sub>EE2</sub> =-8V, OUT1H/L=L |

| Isolation Voltage                       | 2500  | Vrms |                                                         |

| Maximum Operating (Ambient) Temperature | 125   | °C   |                                                         |

| Maximum Junction Temperature            | 150   | °C   |                                                         |

| Maximum Storage Temperature             | 150   | °C   |                                                         |

| Maximum Data Transmission Rate          | 5.5   | MHz  |                                                         |

# **Typical Performance Curves**

Figure 19. Main Power Supply Circuit Current vs Main Power Supply Voltage

Output-side Positive Supply Voltage: V<sub>CC2</sub> [V]

Figure 20. Output-side Circuit Current vs Output-side Positive Supply Voltage (MODE=H, V<sub>EE2</sub>=0V, OUT1=L)

Figure 21. Output-side Circuit Current vs Output-side Positive Supply Voltage (MODE=H, V<sub>EE2</sub>=0V, OUT1=H)

Figure 22. FET\_G ON-resistance vs Temperature (Source /Sink)

Figure 23. Oscillation Frequency vs RT Resistance

Figure 24. Soft-start Time vs Temperature

Figure 25. FB Pin Threshold Voltage vs Temperature

Figure 26. COMP Pin Sink Current vs Temperature

Figure 27. COMP Pin Source Current vs Temperature

Figure 28. Over Current Detection Threshold vs Temperature

Figure 29. Logic Input Filtering Time vs Temperature (L pulse)

Figure 30. Logic Input Filtering Time vs Temperature (H pulse)

Figure 31. ENA Input Filtering Time Figure vs Temperature

Figure 32. MODE Input Voltage vs Temperature  $(V_{CC2}=14V)$

Figure 33. OUT1H ON-resistance (Source) vs Temperature (I<sub>OUT1H</sub>=-40mA)

Figure 34. OUT1L ON-resistance (Sink) vs Temperature (I<sub>OUT1L</sub>=40mA)

Figure 35. PROOUT ON-resistance vs Temperature (I<sub>PROOUT</sub>=40mA)

Figure 36. Turn ON time vs Temperature

Figure 37. Turn OFF time vs Temperature

Figure 38. OUT2 ON-resistance vs Temperature (I<sub>OUT2</sub>=40mA)

Figure 39. Short Current Detection Voltage vs Temperature

Figure 40. DESAT Leading Edge Blanking Time vs Temperature

Figure 41. Short Current Detection Filter Time vs Temperature

Figure 42. Short Current Detection Delay Time (PROOUT) vs Temperature

Figure 43. SCPIN Pin Low Voltage vs Temperature

Figure 44. Output Delay Difference between PROOUT and FLT vs Temperature

Figure 45. Thermal Detection Voltage vs Temperature

Figure 46. Recommended External Parts

I/O Equivalence Circuits

| Pin No. | Pin Name                                   | Input Output Equivalent Circuit Diagram |

|---------|--------------------------------------------|-----------------------------------------|

| PIN NO. | Pin Function                               | Input Output Equivalent Circuit Diagram |

|         | PROOUT                                     | VCC2                                    |

| 2       | Soft turn-off pin/Gate voltage input pin   | PROOUT  VEE2                            |

| 2       | VTSIN                                      | VCC2                                    |

| 3       | Temperature sensor voltage input pin       | VTSIN GND2                              |

| 4       | SCPIN  Short circuit current detection pin | VCC2                                    |

| 4       |                                            | GND2                                    |

|         | MODE                                       | VCC2                                    |

| 7       | Mode selection pin of output-side UVLO     | MODE  GND2  VEE2                        |

|         | UVLOIN                                     | VCC2                                    |

| 8       | Output-side UVLO setting input pin         | GND2 VEE2                               |

|         | ence Circuits - continued Pin Name |                                         |

|---------|------------------------------------|-----------------------------------------|

| Pin No. | Pin Function                       | Input Output Equivalent Circuit Diagram |

|         | OUT1H                              | O VCC2                                  |

| 11      | Source side output pin             | OUT1H                                   |

| 12 -    | OUT1L                              | O OUT1L                                 |

| 12      | Sink side output pin               | VEE2                                    |

| 13      | OUT2                               | VCC2                                    |

| 13      | Output pin for Miller Clamp        | VEE2                                    |

|         | FLT                                |                                         |

| 16      | Fault output pin                   | FLT RDY                                 |

|         | RDY                                |                                         |

| 20      | Ready output pin                   | GND1                                    |

|         | ENA                                | VREG                                    |

| 17      | Input enabling signal input pin    | GND1                                    |

| I/O Equivale | ence Circuits - continued                                    |                                         |

|--------------|--------------------------------------------------------------|-----------------------------------------|

| Pin No.      | Name                                                         | Input Output Equivalent Circuit Diagram |

|              | Function                                                     | par o a.par Equitation on our Diagram   |

| 18           | INA                                                          | VREG O                                  |

| 18           | Control input pin A                                          | GND1                                    |

| 19           | INB                                                          | VREG O                                  |

|              | Control input pin B                                          | GND1                                    |

| 21           | RT                                                           | V_BATTO                                 |

|              | Switching frequency setting pin for switching controller     | GND1                                    |

| 22           | FB                                                           | V_BATT Internal power supply            |

| - 22         | Error amplifier inverting input pin for switching controller | GND1 GND1                               |

I/O Equivalence Circuits - continued

| I/O Equivale | ence Circuits – continued                           |                                         |  |  |  |  |  |

|--------------|-----------------------------------------------------|-----------------------------------------|--|--|--|--|--|

| Pin No.      | Name                                                | Input Output Equivalent Circuit Diagram |  |  |  |  |  |

|              | Function                                            |                                         |  |  |  |  |  |

| 23           | СОМР                                                | V_BATT Internal power supply  COMP      |  |  |  |  |  |

|              | Error amplifier output pin for switching controller | GND1 GND1                               |  |  |  |  |  |

| 25           | VREG                                                | Internal power V_BATT                   |  |  |  |  |  |

|              | Input-side internal power supply pin                | vreg                                    |  |  |  |  |  |

|              | FET_G                                               | FET_G                                   |  |  |  |  |  |

| 26           | MOS FET control pin for switching controller        | GND1                                    |  |  |  |  |  |

| 27           | SENSE                                               | V_BATT Internal power supply            |  |  |  |  |  |

| 27           | Current detection pin for switching controller      | SENSE W                                 |  |  |  |  |  |

# **Operational Notes**

# 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply pins.

# 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

# 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

# 5. Recommended Operating Conditions

The function and operation of the IC are guaranteed within the range specified by the recommended operating conditions. The characteristic values are guaranteed only under the conditions of each item specified by the electrical characteristics.

### 6. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

### 7. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

# 8. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

# **Operational Notes - continued**

### 9. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

# 10. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

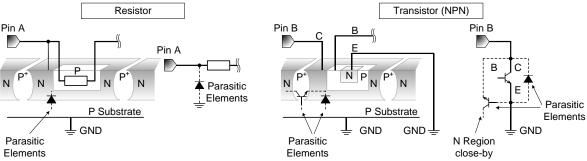

# 11. Regarding the Input Pin of the IC

This IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

Figure 47. Example of IC structure

# 12. Ceramic Capacitor

When using a ceramic capacitor, determine a capacitance value considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

### 13. Area of Safe Operation (ASO)

Operate the IC such that the output voltage, output current, and the maximum junction temperature rating are all within the Area of Safe Operation (ASO).

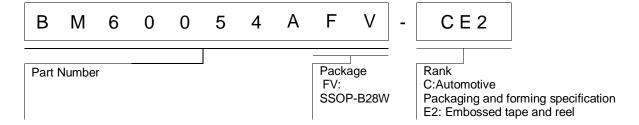

# **Ordering Information**

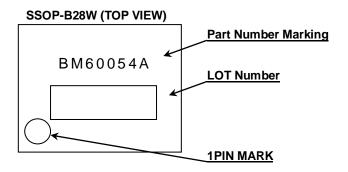

# **Marking Diagram**

**Physical Dimension, Tape and Reel Information**

# **Revision History**

| Date        | Revision | Changes                                                                                                                                                                                                                                                                         |  |  |

|-------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 26.Feb.2018 | 001      | New Release                                                                                                                                                                                                                                                                     |  |  |

| 19.Mar.2018 | 002      | P1 Features : add UL1577 Recognized P17 Absolute Maximum Ratings : delete condition Ta=25°C P19 Change spec of Output-side Circuit Current 5 P20 Change spec of Thermal Detection Voltage P21 Adding UL1577 Rating Table P28 Update Figure 45                                   |  |  |

| 23.Apr.2018 | 003      | P18 Misprint correction of Thermal Resistance                                                                                                                                                                                                                                   |  |  |

| 13.Sep.2019 | 004      | P6 Miller Clamp Function add comment, Figure 4. change Timing chart P10 Figure 10. change Timing chart P15 I/O Condition Table change No.8 P30 I/O Equivalence Circuits change PROOUT,VTSIN P31 I/O Equivalence Circuits change OUT2,ENA P32 I/O Equivalence Circuits change RT |  |  |

# **Notice**

# **Precaution on using ROHM Products**

1. If you intend to use our Products in devices requiring extremely high reliability (such as medical equipment (Note 1), aircraft/spacecraft, nuclear power controllers, etc.) and whose malfunction or failure may cause loss of human life, bodily injury or serious damage to property ("Specific Applications"), please consult with the ROHM sales representative in advance. Unless otherwise agreed in writing by ROHM in advance, ROHM shall not be in any way responsible or liable for any damages, expenses or losses incurred by you or third parties arising from the use of any ROHM's Products for Specific Applications.

(Note1) Medical Equipment Classification of the Specific Applications

| ſ | JÁPAN   | USA     | EU         | CHINA    |

|---|---------|---------|------------|----------|

| Ī | CLASSⅢ  | CLASSII | CLASS II b | CLASSIII |

| ſ | CLASSIV |         | CLASSⅢ     |          |

- 2. ROHM designs and manufactures its Products subject to strict quality control system. However, semiconductor products can fail or malfunction at a certain rate. Please be sure to implement, at your own responsibilities, adequate safety measures including but not limited to fail-safe design against the physical injury, damage to any property, which a failure or malfunction of our Products may cause. The following are examples of safety measures:

- [a] Installation of protection circuits or other protective devices to improve system safety

- [b] Installation of redundant circuits to reduce the impact of single or multiple circuit failure

- 3. Our Products are not designed under any special or extraordinary environments or conditions, as exemplified below. Accordingly, ROHM shall not be in any way responsible or liable for any damages, expenses or losses arising from the use of any ROHM's Products under any special or extraordinary environments or conditions. If you intend to use our Products under any special or extraordinary environments or conditions (as exemplified below), your independent verification and confirmation of product performance, reliability, etc, prior to use, must be necessary:

- [a] Use of our Products in any types of liquid, including water, oils, chemicals, and organic solvents

- [b] Use of our Products outdoors or in places where the Products are exposed to direct sunlight or dust

- [c] Use of our Products in places where the Products are exposed to sea wind or corrosive gases, including Cl<sub>2</sub>, H<sub>2</sub>S, NH<sub>3</sub>, SO<sub>2</sub>, and NO<sub>2</sub>

- [d] Use of our Products in places where the Products are exposed to static electricity or electromagnetic waves

- [e] Use of our Products in proximity to heat-producing components, plastic cords, or other flammable items

- [f] Sealing or coating our Products with resin or other coating materials

- [g] Use of our Products without cleaning residue of flux (Exclude cases where no-clean type fluxes is used. However, recommend sufficiently about the residue.); or Washing our Products by using water or water-soluble cleaning agents for cleaning residue after soldering

- [h] Use of the Products in places subject to dew condensation

- 4. The Products are not subject to radiation-proof design.

- 5. Please verify and confirm characteristics of the final or mounted products in using the Products.

- 6. In particular, if a transient load (a large amount of load applied in a short period of time, such as pulse, is applied, confirmation of performance characteristics after on-board mounting is strongly recommended. Avoid applying power exceeding normal rated power; exceeding the power rating under steady-state loading condition may negatively affect product performance and reliability.