# DataSheet

# AS3940 2.4 GHz Low Power Multi-Channel FSK Transceiver

# 1 General Description

The AS3940 is a highly integrated low power FSK transceiver for wireless communication in the worldwide 2.4 GHz ISM band. It supports data transfer in burst mode and streaming mode at data rates up to 2 Mbit/s.

All communication with a MCU and all configuration of the transceiver can be done using a bidirectional 4 pin serial data interface (SDI).

The integrated timers and link manager enable very low average current consumption in operation and standby and help to reduce overall system cost by eliminating the need for a complex microcontroller (MCU).

Optimum MCU clock frequency can be obtained from a programmable glitch-free clock output derived from the 16 MHz reference crystal oscillator.

The integrated link manager controls all power management modes, like power-down, standby, sleep, wakeup, and data mode, which enable to save power.

The link manager handles all data and frame management in a star network (one master and up to 8 clients) using four separate 256-bit data buffers; two for RX and two for TX. This decreases MCU workload and ensures a smooth data transfer and correct protocol handling. All low level transmission codec and CRC generation is done internally. Microcontroller controlled data transfer (MCDT) mode enables support of proprietary protocols.

Excellent blocking and sensitivity, pseudorandom allocation of communication time slots and the adaptive channel switching enable reliable data transmission and high resistance to interferers like WLAN or Bluetooth.

The high level of integration eliminates the need for external components like battery monitoring circuitry, additional high frequency crystal, and power-on-reset circuitry.

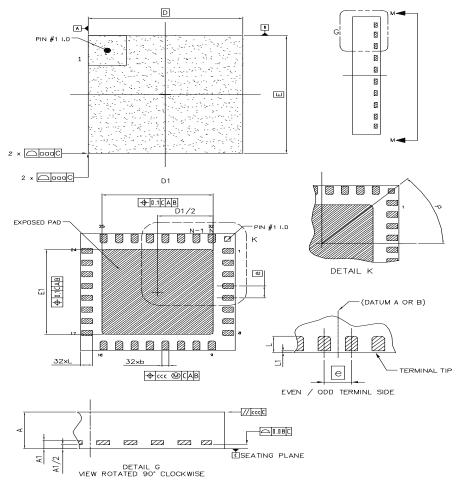

The product is available in a QFN 32 pin (5mm x 5mm) package.

# 2 Key Features

- Fully integrated FSK transceiver

- Operating frequency 2405 to 2480 MHz

- Minimum channel spacing 1MHz

- Data rates in burst mode 250, 1000, 2000 kbps

- Net data rate in streaming mode up to 1000 kbps

- Sensitivity of -100dBm@250kbps, -95.5dBm@1000kbps, and -92.5dBm@2000kbps

- Excellent adjacent channel rejection and blocking performance

- Package synchronized digital RSSI

- Integrated real-time-clock (RTC), 32 kHz XTAL oscillator / calibrated 6.25 kHz derived from a RCO

- Glitch-free CMOS compatible reference clock output 8/4/2/1 MHz or 6.25 kHz

- Output power programmable in 3dB steps (-24 dBm to 0 dBm)

- Integrated Gaussian filter, PLL and loop filter

- 4 separate 256-bit user data buffers (2 x RX, 2 x TX)

- Power on reset (POR, NPOR) for reliable system start

- Battery voltage detection

- Link manager for reliable control of star network (up to 8 clients)

- Device ID recognition and 16-bit CRC computation

- Pairing and automatic (re-)synchronization

- Power-optimized wakeup modes

- Programmable auto-acknowledgement and re-transmit

- Adaptive channel switching / support of frequency hopping

- Programmable timers to define time slots for communication

- Pseudorandom allocation of time slots

# 3 Applications

The AS3940 is ideal for low-power short range devices, body area networks (health, fitness), simple control networks (industry, home), and interactive remote controls.

Data Sheet - Applications

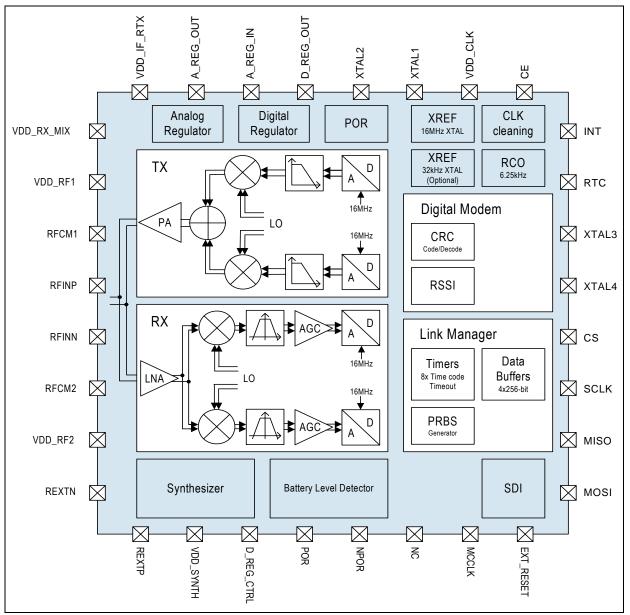

#### Figure 1. Block diagram AS3940

# Contents

| 1 | General Description                            | 1  |

|---|------------------------------------------------|----|

| 2 | Key Features                                   | 1  |

| 3 | Applications                                   | 1  |

| 4 | Pin Assignment                                 | 5  |

|   | 4.1 Pin Description                            | 5  |

| 5 | Absolute Maximum Ratings                       |    |

|   | Electrical Characteristics                     |    |

| U | 6.1 Electrical System Specifications           |    |

|   | 6.2 POR                                        |    |

| 7 | Detailed Description                           |    |

| ' | •                                              |    |

|   | 7.1 Link Manager                               |    |

|   | 7.1.1 Network                                  |    |

|   | 7.1.2 Operation Modes                          |    |

|   | 7.2 Link Manager Short Communication Manual    |    |

|   | 7.2.1 General Settings                         |    |

|   | 7.2.2 Pairing                                  |    |

|   | 7.2.3 Wakeup                                   |    |

|   | 7.2.4 Data Communication                       |    |

|   | 7.3 Detailed Link Manager Protocol Description |    |

|   | 7.3.1 Time Code                                |    |

|   | 7.3.2 Communication Mode                       |    |

|   | 7.3.3 Frequency Channels                       |    |

|   | 7.3.4 RSSI                                     |    |

|   | 7.3.5 Data Package Structure                   |    |

|   | 7.3.6 System Timing Error                      |    |

|   | 7.3.7 Pairing                                  |    |

|   | 7.3.8 Wakeup<br>7.3.9 Communication            |    |

|   | 7.3.10 Data Streaming                          |    |

|   | 7.3.11 Adaptive Channel Switching              |    |

|   | 7.3.12 MCU Controlled Data Transfer (MCDT)     |    |

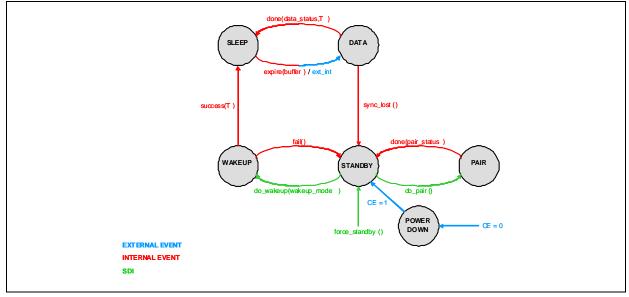

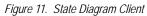

|   | 7.3.13 State Diagrams                          |    |

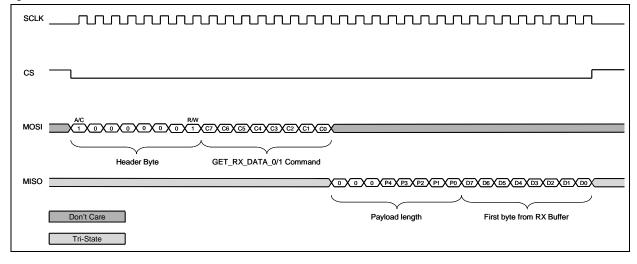

| 8 | SDI Description                                |    |

| Ũ | 8.1 SPI Command Information                    |    |

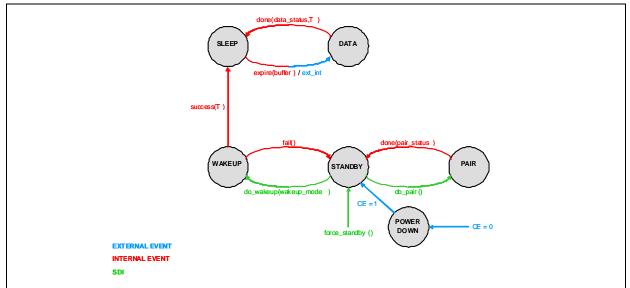

|   | 8.1.1 Write Cycle                              |    |

|   | 8.1.2 Read Cycle                               |    |

|   | 8.1.3 Command Cycle                            |    |

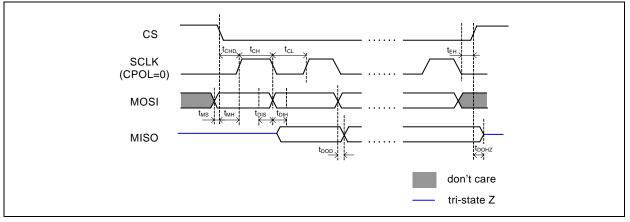

|   | 8.1.4 SPI Timings                              |    |

|   | 8.2 SDI Memory Map                             |    |

|   | 8.2.1 Memory Map Overview                      |    |

|   | 8.2.2 Commands                                 |    |

|   | 8.2.3 Memory Map                               |    |

|   | 8.2.4 Register Description                     |    |

| 9 | Application Information                        |    |

|   |                                                |    |

| 1 | ) Package Drawings and Markings                | 10 |

Data Sheet - Contents

| 11 | Ordering Information | 71 | l |

|----|----------------------|----|---|

|----|----------------------|----|---|

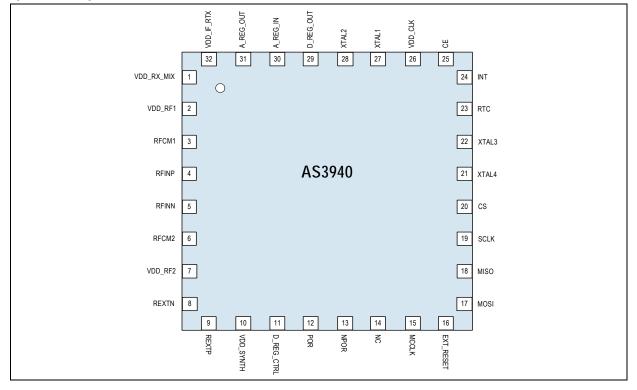

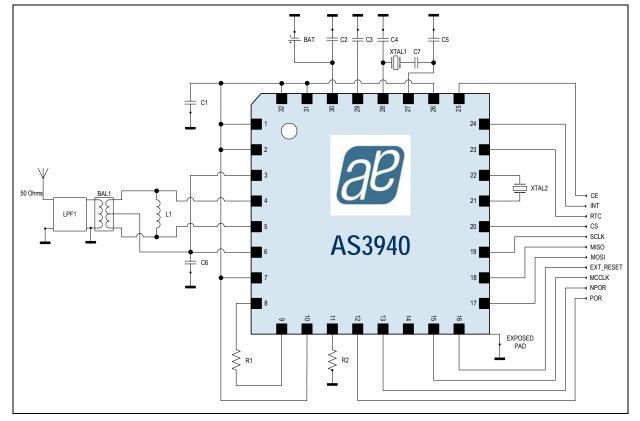

# 4 Pin Assignment

Figure 2. Pin Assignment

# 4.1 Pin Description

Table 1. Pin Description

| Pin Name   | Pin<br>Number | Pin Type | Supply                                   | Description                                     |

|------------|---------------|----------|------------------------------------------|-------------------------------------------------|

| Vdd_RX_MIX | 1             | S        | Voltage input<br>1.9V ± 0.1V             | VDD for IF part of RX and BB part of TX         |

| Vdd_RF1    | 2             | S        | Voltage input<br>1.9V ± 0.1V             | VDD for LNA and PA                              |

| RFCM1      | 3             | AIO      | Voltage output<br>TX: 1.9V<br>RX: ≈170mV | Common Mode voltage output for matching network |

| RFINP      | 4             | AIO      | $200\Omega$ differential                 | Antenna input/output                            |

| RFINN      | 5             | AIO      | $200\Omega$ differential                 | Antenna input/output                            |

| RFCM2      | 6             | AIO      | Voltage output<br>TX: 1.9V<br>RX: ≈170mV | Common Mode voltage output for matching network |

| Vdd_RF2    | 7             | S        | Voltage input<br>1.9V ± 0.1V             | VDD for LNA and PA                              |

| REXTN      | 8             | AIO      | 560 Ω                                    | Esternel register for bigging                   |

| REXTP      | 9             | AIU      | 500 22                                   | External resistor for biasing                   |

| Vdd_SYNTH  | 10            | S        | Voltage input<br>1.9V ± 0.1V             | VDD for synthesizer                             |

#### Table 1. Pin Description

| Pin Name    | Pin<br>Number   | Pin Type | Supply                                                                      | Description                                                                                                                                                                                            |  |

|-------------|-----------------|----------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|             |                 |          | Voltage input<br>If GND><br>D_REG_OUT=<br>1.6V                              | When tied to ground, the digital regulator is forced to 1.6V typ. supply voltage even during the device read access.                                                                                   |  |

| D_REG_CTRL  | A<br>><br>1.65' |          | If NC or<br>A_REG_OUT<br>> D_REG_OUT=<br>1.65Vmin during the<br>device read | When left unconnected or tied high to the analog regulator output (1.9V typ.), the digital regulator will increase its voltage to at least 1.65V worst case (1.7V typ.) during the device read access. |  |

| POR         | 12              | AIO      |                                                                             | Digitally delayed POR active high                                                                                                                                                                      |  |

| NPOR        | 13              | AIO      |                                                                             | Digitally delayed POR active low                                                                                                                                                                       |  |

| NC          | 14              |          |                                                                             |                                                                                                                                                                                                        |  |

| MCCLK       | 15              | DO       |                                                                             | Clock for MCU (8/4/2/1 MHz or 6.25 kHz)                                                                                                                                                                |  |

| EXT_RESET   | 16              | DI       |                                                                             | Reset signal from MCU, active low                                                                                                                                                                      |  |

| MOSI        | 17              | DI       |                                                                             | SPI Master out slave in                                                                                                                                                                                |  |

| MISO        | 18              | DO_T     |                                                                             | SPI Master in slave out                                                                                                                                                                                |  |

| SCLK        | 19              | DI       |                                                                             | SPI clock                                                                                                                                                                                              |  |

| CS          | 20              | DI       |                                                                             | SPI chip select, active low                                                                                                                                                                            |  |

| XTAL4       | 21              | AIO      |                                                                             | XTAL                                                                                                                                                                                                   |  |

| XTAL3       | 22              | AIO      |                                                                             | XTAL                                                                                                                                                                                                   |  |

| RTC         | 23              | DO       |                                                                             | Real time clock/RCO (32/6.25 kHz)                                                                                                                                                                      |  |

| INT         | 24              | DO       |                                                                             | Interrupt to MCU, active low                                                                                                                                                                           |  |

| CE          | 25              | DI       |                                                                             | Chip enable, active high                                                                                                                                                                               |  |

| Vdd_CLK     | 26              | S        | Voltage input<br>1.9V ± 0.1V                                                | VDD for XTAL oscillator or clock divider, and ADC                                                                                                                                                      |  |

| XTAL1       | 27              | AIO      |                                                                             | XTAL sense<br>27pF to ground                                                                                                                                                                           |  |

| XTAL2       | 28              | AIO      |                                                                             | XTAL drive<br>33pF to ground                                                                                                                                                                           |  |

| D_REG_OUT   | 29              | S        | 1.6V                                                                        | decoupling pin for digital VDD                                                                                                                                                                         |  |

| A_REG_IN    | 30              | S        | $2.2 \rightarrow 3.6V$                                                      | Positive Supply voltage                                                                                                                                                                                |  |

| A_REG_OUT   | 31              | S        | Voltage output<br>1.9V ± 0.1V                                               | Stabilized analog supply voltage output                                                                                                                                                                |  |

| VDD_IF_RTX  | 32              | S        | Voltage input<br>1.9V ± 0.1V                                                | VDD for IF strip, TX mixers and both I/Q dividers                                                                                                                                                      |  |

| Exposed Pad |                 |          | GND                                                                         | Exposed Pad must me grounded                                                                                                                                                                           |  |

**Note:** The following are the Pin Types

- S: supply pad

- AIO: analog I/O

- DI: digital input

- DO\_T: digital output / tristate

- DO: digital output

# 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Section 6 Electrical Characteristics on page 8 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Parameter                                     | Min  | Max | Unit | Note                                                                                                                                            |

|-----------------------------------------------|------|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| DC supply voltage (VDD)                       | -0.5 | 3.6 | V    | Only a_reg_in                                                                                                                                   |

| Input pin voltage (VIN)                       | -0.5 | 3.6 | V    | Only digital I/O, XTAL3, XTAL4, POR, NPOR.<br>The rating for the remaining analog I/O's is 2V.<br>V <sub>in</sub> should not exceed VDD + 0.5V. |

| Input current (latchup immunity) Iscr         | -100 | 100 | mA   | Norm: Jedec 78                                                                                                                                  |

| ESD for digital pins (ESDO)                   | ±2   |     | kV   | Norm: MIL 883 E method 3015 (Human Body Model)                                                                                                  |

| ESD for analog pins (ESDA)                    | ±2   |     | kV   | Norm: MIL 883 E method 3015 (Human Body Model)                                                                                                  |

| ESD for RF pins (ESDRF)                       | ±2   |     | kV   | Norm: MIL 883 E method 3015 (Human Body Model)                                                                                                  |

| Storage temperature (T <sub>strg</sub> )      | -55  | 125 | °C   |                                                                                                                                                 |

| Package body temperature (T <sub>body</sub> ) |      | 260 | ℃    | Norm: IPC/JEDEC J-STD-020C <sup>1,2</sup>                                                                                                       |

| Humidity non-condensing                       | 5    | 85  | %    |                                                                                                                                                 |

1. The reflow peak soldering temperature (body temperature) is specified according IPC/JEDEC J-STD-020C "Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices".

2. The lead finish for Pb-free leaded packages is "Matte Tin" (100% Sn).

# 6 Electrical Characteristics

Table 3. Electrical Characteristics

| Symbol                   | Parameter                            | Condition                                                                                          | Min                   | Тур  | Max | Units            |

|--------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------|------|-----|------------------|

| Recommended O            | perating Conditions                  |                                                                                                    |                       |      |     |                  |

| Vdd                      | Positive Supply voltage <sup>1</sup> |                                                                                                    | 2.2                   | 3.0  | 3.6 | V                |

| Vddripple                | Positive Supply voltage ripple       |                                                                                                    |                       |      | 2   | mV <sub>pp</sub> |

| Тамв                     | Ambient temperature                  |                                                                                                    | -40                   |      | 85  | °C               |

|                          | Chip temperature                     |                                                                                                    | -40                   |      | 95  | °C               |

| f <sub>clk</sub>         | System clock frequency               |                                                                                                    | 16                    |      |     | MHz              |

| Current Consump          | tion Specifications                  | •                                                                                                  | <u> </u>              |      |     |                  |

| I <sub>PD</sub>          | POWER-DOWN mode                      | Leakage currents, weak digital regulator<br>running                                                |                       | 1.5  |     | μA               |

| ISLEEP                   | SLEEP mode, 32kHz XTAL               | If clock provided to the RTC pin, additional current is $0.3\mu A + 0.1\mu A/pF$                   |                       | 4.1  |     | μA               |

| I <sub>SLEEP</sub>       | SLEEP mode, RCO                      | If clock provided to the RTC pin,<br>additional current is 0.3μA + 0.1μA/pF                        |                       | 2.9  |     | μA               |

| I <sub>SB</sub>          | STANDBY mode                         | Weak digital regulator, strong digital<br>regulator, analog regulator and 16MHz<br>XTAL are active |                       | 2.0  |     | mA               |

| I <sub>RX</sub>          | RX mode                              |                                                                                                    |                       | 20.9 |     | mA               |

| I <sub>TX</sub> @ 0dBm   | TX mode, 0dBm                        |                                                                                                    |                       | 21.5 |     | mA               |

| I <sub>TX</sub> @ -3dBm  | TX mode, -3dBm                       |                                                                                                    |                       | 19.3 |     | mA               |

| I <sub>TX</sub> @ -24dBm | TX mode, -24dBm                      |                                                                                                    |                       | 14.7 |     | mA               |

| Characteristics fo       | r Digital Inputs and Outputs         |                                                                                                    |                       |      |     |                  |

| CMOS input               | -                                    | -                                                                                                  |                       |      |     | -                |

| VIH                      | High level input voltage             |                                                                                                    | 2                     |      | 3.6 | V                |

| VIL                      | Low level input voltage              |                                                                                                    | -0.3                  |      | 0.8 | V                |

| I <sub>LEAK</sub>        | Input leakage current                | At V <sub>I</sub> = 3.3V or 0V                                                                     | -10                   |      | 10  | μA               |

| CMOS output              |                                      |                                                                                                    |                       |      |     |                  |

| V <sub>OH</sub>          | High level output voltage            | At I <sub>LOAD</sub> = 1mA                                                                         | V <sub>DD</sub> - 0.6 |      |     | V                |

| V <sub>OL</sub>          | Low level output voltage             | At I <sub>LOAD</sub> = 1mA                                                                         |                       |      | 0.4 | V                |

| CL                       | Capacitive load                      |                                                                                                    |                       |      | 50  | pF               |

| Tristate CMOS out        | tput                                 |                                                                                                    |                       |      |     |                  |

| V <sub>OH</sub>          | High level output voltage            |                                                                                                    | V <sub>DD</sub> - 0.6 |      |     | V                |

| V <sub>OL</sub>          | Low level output voltage             |                                                                                                    |                       |      | 0.4 | V                |

| $I_{OZ}^{2}$             | Tristate leakage current             | At $V_O$ = 3.3V or 0 V                                                                             | -10                   |      | 10  | μA               |

|                          | 1                                    |                                                                                                    | 1                     |      |     |                  |

1. The AS3940 is functional down to minimum positive supply voltage of 2.0V, but specifications are not guaranteed

2. The input voltage and the voltage forced on a tristate output should not exceed VDD + 0.3 V in order to meet the 10µA leakage requirement at low supply voltages.

# 6.1 Electrical System Specifications

Table 4. Electrical System Specifications

| Symbol                | Parameter           | Condition                      | Min  | Тур    | Max  | Units |  |  |

|-----------------------|---------------------|--------------------------------|------|--------|------|-------|--|--|

| Modulation            |                     | •                              |      |        |      |       |  |  |

|                       | Modulation method   | BT=0.5                         |      | GFSK   |      |       |  |  |

|                       | Frequency range     |                                | 2405 |        | 2480 | MHz   |  |  |

|                       |                     |                                |      | 250    |      | kbps  |  |  |

|                       | Bit rate            |                                |      | 1000   |      | kbps  |  |  |

|                       |                     |                                |      | 2000   |      | kbps  |  |  |

|                       |                     |                                |      | 160    |      | kHz   |  |  |

|                       | Frequency deviation |                                |      | 320    |      | kHz   |  |  |

|                       |                     |                                |      | 400    |      | kHz   |  |  |

|                       |                     |                                |      | 800    |      | kHz   |  |  |

|                       | Payload data size   | Programmable with 1-Byte steps | 8    |        | 256  | bits  |  |  |

| Receiver <sup>1</sup> |                     |                                |      |        |      |       |  |  |

| Sensitivity           |                     |                                |      |        |      |       |  |  |

|                       | @ 250kbps           | f_dev = 160kHz                 |      | -100.0 |      | dBm   |  |  |

|                       | @ 11/haa            | f_dev = 160kHz                 |      | -89.0  |      | dBm   |  |  |

|                       | @ 1Mbps             | f_dev = 400kHz                 |      | -95.5  |      | dBm   |  |  |

|                       |                     | f_dev = 320kHz                 |      | -85.5  |      | dBm   |  |  |

|                       | – @ 2Mbps           | f_dev = 800kHz                 |      | -92.5  |      | dBm   |  |  |

| Blocking <sup>2</sup> |                     | C/I<br>C = Sensitivity + 3dB   |      |        |      |       |  |  |

| DR = 250kbps, f_c     | lev = 160kHz        |                                |      | -      |      |       |  |  |

|                       | 0 MHz               | CW interferer                  |      | 10.0   |      | dB    |  |  |

|                       | 0 MHz               | Modulated interferer           |      | 10.0   |      | dB    |  |  |

|                       | ± 1MHz              | CW interferer                  |      | -25.0  |      | dB    |  |  |

|                       | ± 1MHz              | Modulated interferer           |      | -25.0  |      | dB    |  |  |

|                       | ± 2MHz              | CW interferer                  |      | -45.0  |      | dB    |  |  |

|                       | ± 2MHz              | Modulated interferer           |      | -30.0  |      | dB    |  |  |

|                       | ± 3MHz              | CW interferer                  |      | -40.0  |      | dB    |  |  |

|                       | ± 3MHz              | Modulated interferer           |      | -45.0  |      | dB    |  |  |

| DR = 1000kbps, f_     | _dev = 160kHz       |                                |      |        | 1    |       |  |  |

|                       | 0 MHz               | CW interferer                  |      | 3.0    |      | dB    |  |  |

|                       | 0 MHz               | Modulated interferer           |      | 13.0   |      | dB    |  |  |

|                       | ± 1MHz              | CW interferer                  |      | -20.0  |      | dB    |  |  |

|                       | ± 1MHz              | Modulated interferer           |      | 0.0    |      | dB    |  |  |

|                       | ± 2MHz              | CW interferer                  |      | -30.0  |      | dB    |  |  |

|                       | ± 2MHz              | Modulated interferer           |      | -20.0  |      | dB    |  |  |

|                       | ± 3MHz              | CW interferer                  |      | -40.0  |      | dB    |  |  |

Data Sheet - Electrical Characteristics

#### Table 4. Electrical System Specifications

| Symbol            | Parameter            | Condition                                               | Min | Тур   | Max | Units |

|-------------------|----------------------|---------------------------------------------------------|-----|-------|-----|-------|

|                   | ± 3MHz               | Modulated interferer                                    |     | -25.0 |     | dB    |

| DR = 1000kbps, f_ | dev = 400kHz         |                                                         |     |       |     |       |

|                   | 0 MHz                | CW interferer                                           |     | 10.0  |     | dB    |

|                   | 0 MHz                | Modulated interferer                                    |     | 10.0  |     | dB    |

|                   | ± 2MHz               | CW interferer                                           |     | -40.0 |     | dB    |

|                   | ± 2MHz               | Modulated interferer                                    |     | -20.0 |     | dB    |

|                   | ± 4MHz               | CW interferer                                           |     | -25.0 |     | dB    |

|                   | ± 4MHz               | Modulated interferer                                    |     | -20.0 |     | dB    |

|                   | ± 6MHz               | CW interferer                                           |     | -55.0 |     | dB    |

|                   | ± 6MHz               | Modulated interferer                                    |     | -55.0 |     | dB    |

| DR = 2000kbps, f_ | dev = 320kHz         | -                                                       |     |       | 1   | 1     |

|                   | 0 MHz                | CW interferer                                           |     | 3.0   |     | dB    |

|                   | 0 MHz                | Modulated interferer                                    |     | 12.0  |     | dB    |

|                   | ± 2MHz               | CW interferer                                           |     | -20.0 |     | dB    |

|                   | ± 2MHz               | Modulated interferer                                    |     | 0.0   |     | dB    |

|                   | ± 4MHz               | CW interferer                                           |     | -30.0 |     | dB    |

|                   | ± 4MHz               | Modulated interferer                                    |     | -20.0 |     | dB    |

|                   | ± 6MHz               | CW interferer                                           |     | -45.0 |     | dB    |

|                   | ± 6MHz               | Modulated interferer                                    |     | -35.0 |     | dB    |

| DR = 2000kbps, f_ | dev = 800kHz         | -                                                       |     |       |     |       |

|                   | 0 MHz                | CW interferer                                           |     | 10.0  |     | dB    |

|                   | 0 MHz                | Modulated interferer                                    |     | 10.0  |     | dB    |

|                   | ± 3MHz               | CW interferer                                           |     | -15.0 |     | dB    |

|                   | ± 3MHz               | Modulated interferer                                    |     | -15.0 |     | dB    |

|                   | ± 6MHz               | CW interferer                                           |     | -50.0 |     | dB    |

|                   | ± 6MHz               | Modulated interferer                                    |     | -30.0 |     | dB    |

|                   | ± 9MHz               | CW interferer                                           |     | -55.0 |     | dB    |

|                   | ± 9MHz               | Modulated interferer                                    |     | -55.0 |     | dB    |

|                   | Maximum input signal |                                                         |     | 10.0  |     | dBm   |

|                   | IP3                  | Measured at the balun input with two carriers of -33dBm |     | -15   |     | dBm   |

| RSSI              |                      |                                                         | •   |       | •   | •     |

|                   | RSSI start           |                                                         |     | -95.0 |     | dBm   |

|                   | RSSI stop            |                                                         |     | -35.0 |     | dBm   |

|                   | RSSI accuracy        |                                                         |     | ±2    |     | dB    |

|                   | RSSI linearity       |                                                         |     | ±0.5  |     | dB    |

|                   | RSSI resolution      |                                                         |     | 0.2   |     | dB    |

Data Sheet - Electrical Characteristics

#### Table 4. Electrical System Specifications

| Symbol                   | Parameter                                                       | Condition                                       | Min  | Тур              | Max  | Units |

|--------------------------|-----------------------------------------------------------------|-------------------------------------------------|------|------------------|------|-------|

| Transmitter <sup>3</sup> | ·                                                               |                                                 |      |                  |      |       |

|                          | TX output power                                                 | Programmable in 3dB steps down to -<br>24dBm    | -24  | 0                | 1.5  | dBm   |

| Spurious Emissio         | ns according to ETSI EN 300 440                                 |                                                 |      |                  |      |       |

|                          | 25MHz1000MHz                                                    | max -36dBm (operation)                          |      | -85              |      | dBm   |

|                          | (RBW=1MHz)                                                      | max -57dBm (standby)                            |      | -85              |      | ubiii |

|                          | 47MHz74MHz,<br>87 5MHz 118MHz                                   | max -54dBm (operation)                          |      | -85              |      |       |

|                          | 87,5MHz118MHz,<br>174MHz230MHz,<br>470MHz862MHz<br>(RBW=100kHz) | max -57dBm (standby)                            |      | -85              |      | dBm   |

|                          |                                                                 | max -30dBm (operation)                          |      | -75<br>@2nd Harm |      | dBm   |

|                          | Otherwise >1000MHz                                              |                                                 |      | -55<br>@3rd Harm |      |       |

|                          |                                                                 | max -47dBm (standby)                            |      | -70              |      |       |

| Spurious Emissio         | ns according to FCC CFR47 Section                               | n 15.249                                        |      |                  |      |       |

|                          | Forbidden bands<br><960MHz<br>(RBW=120kHz)                      | max -49 dBm                                     |      | -85              |      | dBm   |

|                          | Forbidden bands<br>960-1000 MHz<br>(RBW=120kHz)                 | max -41 dBm                                     |      | -85              |      | dBm   |

|                          | Forbidden bands<br>1000MHz2400MHz<br>(RBW=1MHz)                 | max -41dBm<br>fc=2405MHz (modulated signal)     |      | -45<br>@2389 MHz |      | dBm   |

|                          |                                                                 | max -41dBm                                      |      | -45<br>@2496 MHz |      |       |

|                          | Forbidden bands<br>2483.5MHz∞ (RBW=1MHz)                        | fc=2480MHz (modulated signal, CW for harmonics) |      | -75<br>@2nd Harm |      | dBm   |

|                          |                                                                 |                                                 |      | -55<br>@3rd Harm |      |       |

| Spurious Emissio         | ns according to ARIB STD-T66                                    |                                                 |      |                  |      |       |

|                          | <2387MHz<br>(RBW=1MHz)                                          | max -26dBm<br>fc=2405MHz (CW signal)            |      | -60              |      | dBm   |

|                          | 2387-2400MHz (RBW=1MHz)                                         | max -16dBm<br>fc=2405MHz (CW signal)            |      | -70              |      | dBm   |

|                          | 2483.5-2496.5MHz<br>(RBW=1MHz)                                  | max -16dBm<br>fc=2480MHz (CW signal)            |      | -65              |      | dBm   |

|                          | — >2496.5MHz (RBW=1MHz)                                         | max -26dBm                                      |      | -75<br>@2nd Harm |      | dBm   |

|                          |                                                                 | fc=2480MHz (CW signal)                          |      | -55<br>@3rd Harm |      |       |

| Synthesizer              | _                                                               |                                                 | _    |                  |      |       |

| F <sub>synth</sub>       | Frequency range                                                 |                                                 | 2405 |                  | 2480 | MHz   |

|                          | Synthesizer Resolution                                          |                                                 |      | 1                |      | MHz   |

#### Table 4. Electrical System Specifications

| Symbol             | Parameter                                                                                       | Condition                                                                                       | Min | Тур    | Max   | Units  |

|--------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-----|--------|-------|--------|

| CNR@100kHz         |                                                                                                 |                                                                                                 |     | -71    |       | dBc/Hz |

| CNR@1MHz           |                                                                                                 |                                                                                                 |     | -91    |       | dBc/Hz |

| CNR@4MHz           | LO Phase noise                                                                                  |                                                                                                 |     | -103   |       | dBc/Hz |

| CNR@10MHz          |                                                                                                 |                                                                                                 |     | -111   |       | dBc/Hz |

| t <sub>lock</sub>  | PLL Lock time                                                                                   | From channel change or RX/TX switch                                                             |     | 120    |       | μs     |

| Crystal Oscillator | 32 kHz                                                                                          |                                                                                                 |     |        |       |        |

|                    | Recommended crystal accuracy (initial)                                                          | -0.034 ppm/K <sup>2</sup> temperature coefficient not assumed                                   |     |        | ±20   | p.p.m. |

|                    | Recommended frequency                                                                           |                                                                                                 |     | 32.768 |       | kHz    |

|                    | Maximum contribution of the oscillator to the frequency error                                   |                                                                                                 |     | ±10    |       | p.p.m  |

|                    | Minimum Start-up Time                                                                           |                                                                                                 |     | 100    |       |        |

|                    | Typical Start-up Time                                                                           |                                                                                                 |     | 384    |       | ms     |

|                    | Maximum Start-up Time                                                                           |                                                                                                 |     | 1000   |       |        |

|                    | Duty cycle                                                                                      |                                                                                                 |     | 50     |       | %      |

|                    | Duty cycle Variation                                                                            |                                                                                                 |     | ±20    |       | %      |

| Crystal Oscillator | 16 MHz                                                                                          |                                                                                                 |     |        |       |        |

|                    | Recommended crystal accuracy                                                                    | (initial + temp + ageing)                                                                       |     |        | ±40   | p.p.m. |

|                    | Recommended frequency                                                                           |                                                                                                 |     | 16     |       | MHz    |

|                    | Maximum contribution of the oscillator to the frequency error                                   |                                                                                                 |     | ±9     |       | p.p.m  |

|                    | Phase noise at 10kHz distance<br>(noise floor)                                                  | simulated at the output of a noiseless<br>pulse former that only responds to the<br>rising edge |     | -126   |       | dBc/Hz |

|                    | Duty cycle, full settled                                                                        |                                                                                                 |     | 50     |       | %      |

|                    | Duty cycle Variation, full settled                                                              |                                                                                                 |     | ±5     |       | %      |

|                    | Start-up time, full settled                                                                     |                                                                                                 |     | 700    |       |        |

|                    | Maximum Start-up time, full settled                                                             | Depends on crystal properties <sup>4</sup>                                                      |     | 2000   |       | μs     |

| RC Oscillator 6.25 | 5 kHz                                                                                           |                                                                                                 |     |        |       | -      |

|                    | Frequency, calibrated                                                                           |                                                                                                 |     | 6.25   |       | kHz    |

|                    | Maximum frequency error of the<br>calibrated RC Oscillator (without<br>the 16MHz crystal error) |                                                                                                 |     | 100    |       | p.p.m  |

|                    | Typical temperature coefficient of the period time                                              | Specified over 10°C sub-ranges near                                                             |     | -20    | nnm/k |        |

|                    | Maximum temperature<br>coefficient of the period time                                           | 25°C and near the temperature extremes                                                          |     | ±200   |       | ppm/K  |

|                    | Maximum Start-up time                                                                           |                                                                                                 |     | 700    |       | μs     |

1. All RX measurements have been performed with external matching network (see Figure 18).

2. The level of the wanted signal C is set 3dB above the sensitivity level.

3. All TX measurements have been performed with external matching network (see Figure 18).

4. When the AS3940 wakes up, first the analog voltage regulator is enabled, after it settles the digital regulator is enabled and after that settles the crystal oscillator is enabled. When the AS3940 powers down, all three are disabled simultaneously. Therefore, the crystal oscillator is always started from a well-defined state: the low-to-high transition at its enable input always occurs at a moment when the analog supply voltage has already been there for some time. When the oscillator is disabled, the output going to the digital part must shut down immediately, because the strong digital supply is also disabled and circuitry running at 16MHz should not load the weak digital supply.

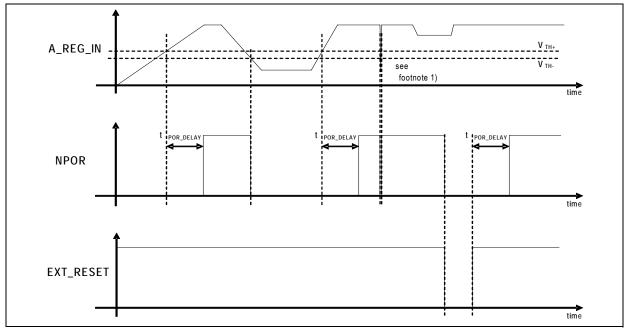

## 6.2 POR

Power-on reset signals, active low (NPOR) and active high (POR), are available for reliable system start-up. Digitally generated delay (tPOR\_DELAY) before the POR is released ensures that the system power supply has stabilized at the appropriate levels and the MCCLK has settled. The POR function can be overwritten by an external RESET signal (default behavior of the EXT\_RESET pin after power-up) from the MCU.

Table 5. Characteristics

| Symbol | Parameter                             | Condition | Min | Тур   | Max | Units |

|--------|---------------------------------------|-----------|-----|-------|-----|-------|

|        | V <sub>TH+</sub>                      |           |     | 1.144 |     | V     |

|        | V <sub>TH-</sub>                      |           |     | 1.130 |     | V     |

|        | Hysteresis                            |           |     | 14    |     | mV    |

|        | tpor_delay                            | 1         | 150 | 200   | 650 | ms    |

|        | Minimum Supply voltage fall time      | 2         |     | 1     |     | ns    |

|        | Minimum Supply_voltage rise time      |           |     | 1     |     | ns    |

|        | Minimum Supply voltage notch<br>width |           |     | 1     |     | ns    |

|        | Output impedance @ POR,<br>NPOR       |           |     | 10    |     | kΩ    |

Data Sheet - Electrical Characteristics

- 1. When the voltage drops from 3.6V to 0V in 144µs (25kV/s) and then immediately rises to 3.6V with a 1µs rise time (3.6A charge current for a 1µF total decoupling capacitance), a POR is generated on the rising edge of battery voltage.

- 2. 1ns narrow dips on VDD are rather unlikely. For example 1µF of decoupling on the power supply and 25mA total supply current, the voltage will not drop faster than by 25kV/s even when the battery gets disconnected.

# 7 Detailed Description

The major parts of AS3940 are receiver (RX), transmitter (TX), synthesizer, digital modem, supporting blocks, and a link manager, these are briefly described below.

- Receiver: The receiver consists of LNA, I/Q down-converting mixers, IF filtering, and two A/D converters.

- Transmitter: The TX consists of DSP generating baseband I/Q-signals, two D/A converters, interpolation filters, I/Q up-converting mixers, and Linear PA.

- Synthesizer: The synthesizer consists of VCO with I/Q output, 16MHz XTAL oscillator, and integrated loop filter.

- Digital Modem: The digital modem consists of modulation/demodulation, CRC, and RSSI.

- Supporting Blocks: The supporting blocks are voltage/current reference, regulator for analog supply, regulator for digital supply, 32.768kHz XTAL oscillator, RC-oscillator with 6.25kHz output, clock cleaning, Power On Reset, bidirectional serial digital interface (SDI), and battery level detector.

- Link Manager: The Link Manager manages the link parameters, the timings, and the adaptive channel switching in order to set-up and to maintain up to 8 communication links simultaneously. All these actions are done automatically and are transparent to the user.

## 7.1 Link Manager

The transceiver is optimized for applications where low power consumption is very critical, and therefore the data transmission is done in small bursts at high data rate which allows the devices to be active only a short period of time and therefore save power.

For a Client transmitting payload data (programmable between 1 and 32 Bytes) every 2s with auto-acknowledgement enabled, the typical average current consumption values are presented in Table 6. The current includes all timing and network administration done internally by the AS3940 Link Manager.

Table 6. Current Consumption

| Data Rate                             | Average Current Consumption     |  |  |

|---------------------------------------|---------------------------------|--|--|

| 250kbps                               | 12.2μA + Payload Bytes * 0.35μA |  |  |

| 1Mbps 5.8µA + Payload Bytes * 0.087µA |                                 |  |  |

| 2Mbps                                 | 4.8μA + Payload Bytes * 0.045μA |  |  |

The link manager has a critical role in receiving and transmitting of the data.

Data transmission: The microcontroller (MCU) supplies data via SDI to an integrated TX data buffer from where the link manager takes the data, adds the needed network management bits (preamble, device ID, time code, and CRC), and enables the transmitter for transmitting the data package at a correct time slot.

Data receiving: The link manager wakes up the receiver at a correct time slot. It checks the CRC of the payload data and if that is correct, it removes all network management bits and stores the data to a RX data buffer. The link manager gives an interrupt to the MCU, which can then retrieve data via SDI.

When the link manager is by-passed (except AS3940 physical layer, framer/de-framer, RX/TX buffering, and CRC computation), all tasks of the link manager must be made by the MCU via commands (see Commands on page 39).

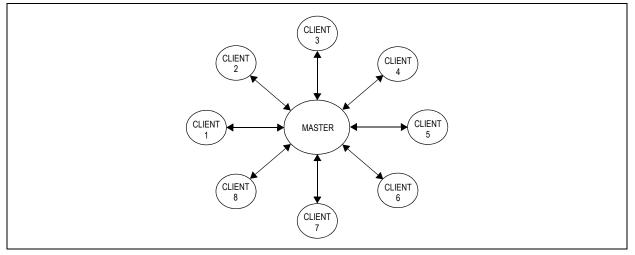

#### 7.1.1 Network

The Link Manager supports a star network which consists of one master and maximum 8 clients like presented in Figure 4. The master acts as a data processor and collector, the clients act as data producers. The master manages the parameters used for communication such as channel frequency, data rate, auto-acknowledgement, re-transmission of lost data, and adaptive channel switching.

#### Figure 4. Star Network

All devices in the network have a unique device ID. A communication link between a master and a client can be established if the master receives the device ID from the known device type. Introduction of new clients to a master, when the master stores the device IDs of the clients, is called pairing. In wakeup the master and the client exchange the RF parameters for communication and synchronize their time bases in order to establish next data exchange simultaneously. If the client is already paired with the master, only wakeup is needed prior communication. The pairing and wakeup procedures are done only at certain application specific frequency channels.

#### 7.1.2 Operation Modes

The following different Link Manager operation modes are supported.

#### 7.1.2.1 Power-down

Power-down mode is entered after connecting the battery. Registers have their default values. Lowest current consumption, only a weak regulator is running to keep the register values. No clock is provided at MCCLK and RTC pin (the MCU must have other CLK source). The CE pin HIGH is needed to switch to standby.

#### 7.1.2.2 Standby

No active communication (idle mode), no connection (no synchronization) established between master and client, SDI operational. Clock can be provided at MCCLK and/or RTC pin (16MHz XTAL and dividers are active). MCCLK and RTC enable/disable required.

#### 7.1.2.3 Pairing

- Permanent pairing: Device IDs are exchanged and permanently stored (can be overwritten).

- Temporary pairing: done for each temporary session, device ID is not permanently stored.

#### 7.1.2.4 Wakeup

Exchange of time code (or seed) and communication parameters, master synchronizes to client time base.

Synchronization can only be done when the master and the client share the same RF channel and communication mode. The prerequisite for synchronization is that pairing has been done.

#### 7.1.2.5 Active

Transmitting or receiving of sensor data. Different communication types: 1-way data transmit, auto-acknowledge, re-transmit of lost data and channel switching.

For temporary pairing applications, the MCU can set the a temporary master to receive mode in order to get data from an active client which is already permanently paired with its own master, without interfering on the previously established communication between master-client.

#### 7.1.2.6 Sleep

Mode between active communication time slots, timers indicate next active communication time slots. Additionally exit by wakeup event is possible for synchronizing of additional sensors. Weak regulator, timers and RCO/32kHz XTAL are running.

# 7.2 Link Manager Short Communication Manual

This chapter explains how to set up a data communication link using the Link Manager and relevant registers. Using default register values offers a functional link, but an experienced user has a freedom to further optimize the settings.

Before a data link can be established, some general settings (see General Settings on page 17) have to be done and the devices must be paired (see Pairing on page 18). Only paired devices can exchange data packages. After pairing, wakeup (see Wakeup on page 19) is needed each time to evoke the data link.

#### 7.2.1 General Settings

#### 7.2.1.1 Clock Settings

Default value: 0x00=66 (if no MCCLK/RTC clocks needed and 32.768kHz available for AS3940 timer clock, then set 0x00 = 01) Default value: 0x01=09 (if no clock needed during sleep, then set 0x01 = 01-07 depending on the used timer tolerance)

RCO, MCCLK, RTC, and AS3940 internal timer clock settings are set via clk\_control registers.

The default value of the registers are set after applying the battery to the AS3940 and after a '1' at the CE pin (pin 25). By default, MCCLK is enabled and set to 1 MHz (6.25kHz during sleep), RTC is enabled and set to 6.25 kHz, AS3940 timer clock is set to 6.25 kHz, 32.768 kHz oscillator is disabled, and the timer tolerance is set to +/- 50ppm.

#### 7.2.1.2 Interrupt Masking

#### Default value: 0x02...0x04=00

Masking of interrupts which can activate the INT pin (pin 24). After the interrupt signal becomes active, additional information on the source of the interrupt can be retrieved via int\_status registers (0x05, 0x06, and 0x07).

After reading one of the int\_status registers, the content of that specific register is cleared.

#### 7.2.1.3 Device Table

#### Default value: 0x10...0x23=00

During reception of any type of AS3940 package, the RX data path is only sensitive to information received from the device types set in the device table. In total a table of 10 supported 2-byte device types is available for initial filtering of any incoming packages.

For device types where the level shifts only once or is constant (e.g. 0000, FFFF, 000F) can often be detected in noise and can give a false detection. This may cause non-functional pairing/wakeup and increased packet error rate during the data communication. It is recommended to set non-zero values for all device types in the device type table, even for the unused device type table entries.

#### 7.2.1.4 Device data

#### Default value: 0xA6...0xAD=FF

The RSSI alignment value must be stored to the device\_data register 0xA6, the CRC initial value to 0xA7...0xA8, and the full device ID (2-byte device type and 3-byte serial number) to 0xA9...0xAD after every power up.

#### 7.2.1.5 Pair/wake Table

Default value: 0x90=05 Default value: 0x91=00 Default value: 0x92=10 Default value: 0x93=00 Default value: 0x94=00 Default value: 0x95=0A Default value: 0x96=0F

The pair/wake table settings, used for pairing (see Pairing on page 18) and wakeup (see Wakeup on page 19), must be the same for the master and all possible own clients. These settings are the pairing/wakeup frequency channel (ICF), communication mode (COM), time code scaling, transmitted power level (PA), timecode, number of wake packages, and trial\_max.

#### 7.2.1.6 General Link Manager Settings

Default value: 0x97=1E (for the Client, set 0x97 = 1F for the Master) Default value: 0x98=8F Default value: 0x99=80 Default value: 0x9A=00 Data Sheet - Detailed Description

General purpose link manager settings set the Tpolmax, CRC normal/reverse, receiver on time and duty cycle, device defined as master/client, 16MHZ XTAL startup time, synh\_lost, temporary pairing package sensitivity, battery level threshold, battery level above/below the threshold, enabling of RSSI check, enabling of CRC interpretation, enabling of smart\_cal, EOC and unpair request, and client selection for EOC/unpair/LIB packages.

For the optimized operation of AS3940, the following addresses must be updated from the default values.

- 0xB1=0A

- 0xE1=69

- 0xE2=24

- 0xE3=58

These settings set the receiver into high gain mode for the highest sensitivity and the transmitter output power to 0dBm. Also, the correlator threshold register 0xB1 is set to avoid false triggering to noise without sacrificing the sensitivity.

#### 7.2.2 Pairing

Pairing is a procedure where master and client exchange their device IDs that is required prior to any data transmission. The pairing command (do\_pair = 0C) starts the procedure.

Common frequency channel and communication mode must be set in the Pair/wake Tables (see General Settings on page 17) of all devices which have to be paired. After successful pairing, the device serial number is stored to the first free client table position and the pairing bit is set. Reading the pairing bit, the device type index, and the corresponding serial number in the SPI register map reveals the paired devices.

7.2.2.1 Pairing bits:

0x33 client\_0\_6<3>=0 Client 0 not paired 0x33 client\_0\_6<3>=1 Client 0 paired 0x3D client\_1\_6<3>=0 Client 1 not paired 0x3D client\_1\_6<3>=1 Client 1 paired

... 0x79 client\_7\_6<3>=0 Client 7 not paired

0x79 client\_7\_6<3>=1 Client 7 paired

7.2.2.2 Device type index:

0x30 client\_0\_9<7:4> Device type index for Client 0 0x3A client\_1\_9<7:4> Device type index for Client 1

...

0x76 client\_7\_9<7:4> Device type index for Client 7

#### 7.2.2.3 Serial numbers:

0x30 client\_0\_9<3:0> Client 0 serial number<23:20> 0x31 client\_0\_8<7:0> Client 0 serial number<19:12> 0x32 client\_0\_7<7:0> Client 0 serial number<11:4> 0x33 client\_0\_6<7:4> Client 0 serial number<3:0> 0x3A client\_1\_9<3:0> Client 1 serial number<23:20> 0x3B client\_1\_8<7:0> Client 1 serial number<19:12> 0x3C client\_1\_7<7:0> Client 1 serial number<11:4> 0x3D client\_1\_6<7:4> Client 1 serial number<3:0>

...

0x76 client\_0\_9<3:0> Client 7 serial number<23:20>

0x77 client\_0\_8<7:0> Client 7 serial number<19:12>

0x78 client\_0\_7<7:0> Client 7 serial number<11:4>

0x79 client\_0\_6<7:4> Client 7 serial number<3:0>

On the master side, the serial number of each paired client is stored. On the client side, the serial number of the master is stored in the client 0 location. One master can be paired with up to 8 clients. A client can be paired with 1 permanent master and with 1 temporary master (the serial number of the temporary master is stored in the client 1 location, the client 1 pairing bit is cleared after a temporary communication session).

Data Sheet - Detailed Description

### 7.2.3 Wakeup

Wakeup is a procedure where master determines the used data communication parameters and synchronizes to the client time base. The wakeup command (do\_wakeup = 08, do\_wakeup\_from\_client = 09, or do\_wakeup\_from\_master = 0A) starts the procedure. Common frequency channel and communication mode must be set in the Pair/wake Tables (see General Settings on page 17) of all devices. After successful wakeup, the wake bit and the sync bit are set.

Reading the wake bit and the sync bit in the SPI register map reveals the waked devices.

7.2.3.1 Wake bits:

0x33 client\_0\_6<0>=0 Client 0 not waked up 0x33 client\_0\_6<0>=1 Client 0 waked up 0x3D client\_1\_6<0>=0 Client 1 not waked up 0x3D client\_1\_6<0>=1 Client 1 waked up

... 0x79 client\_7\_6<0>=0 Client 7 not waked up 0x79 client\_7\_6<0>=1 Client 7 waked up Sync bits: 0x34 client\_0\_6<7>=0 Client 0 in sync 0x34 client\_0\_6<7>=1 Client 0 sync lost 0x3E client\_1\_6<7>=0 Client 1 in sync

0x3E client\_1\_6<7>=1 Client 1 sync lost ... 0x7A client 7\_6<7>=0 Client 7 in sync

0x7A client\_7\_6<7>=1 Client 7 sync lost

#### 7.2.4 Data Communication

The link manager wakes up the devices at correct time point and, if enabled, automatically re-transmits lost data packages and manages the Adaptive Channel Switching (ACS).

The frame management is done using four separate 32-byte data buffers; 2 for RX and 2 for TX. The link manager switches between the buffers to ensure maximum data throughput (see Communication on page 30). The MCU is responsible to write the TX data buffer before the actual communication time slot, and to read the RX data buffer before the data is overwritten.

#### 7.2.4.1 Data reception:

The MCU is informed about received data packages via the following interrupts (if not masked):

0x05 rx\_data\_done\_1<5>=1 Data received in RX buffer 1

0x05 rx\_data\_done\_0<4>=1 Data received in RX buffer 0

0x05 rx\_data\_failed<2>=1 Data reception failed

CRC check of the received data is always done (recommended default setting, 0x9A b[6]=0) and the CRC\_ok / CRC\_not\_ok flag is set in the appropriate client table.

0x9A CRC\_interpret\_disable<6>=0 If the CRC fails, rx\_data\_0/1 interrupt is not set and the buffer selection stays on the current RX buffer 0x9A CRC\_interpret\_disable<6>=1 If the CRC fails, rx\_data\_0/1 interrupt is anyway set and the buffer selection switches to the other RX buffer

#### 7.2.4.2 Data transmission:

The MCU is informed about the success of the transmission via the following interrupts (if not masked):

0x05 tx\_data\_done\_1<7>=1 Data transmitted from TX buffer 1

0x05 tx\_data\_done\_0<6>=1 Data transmitted from TX buffer 0

0x05 tx\_data\_failed<3>=1 Data transmission failed

If both TX buffers contain old data, the selected buffer is not changed. If the unselected buffer contains new data, it will be used for the next transmission.

Reading the buffer status bits in the SPI register map reveals the usage of the buffers.

0x0A buffer\_status<3>=0 TX buffer 0 selected by the link manager

0x0A buffer\_status<3>=1 TX buffer 1 selected by the link manager

0x0A buffer\_status<2>=0 RX buffer 0 selected by the link manager

0x0A buffer\_status<2>=1 RX buffer 1 selected by the link manager 0x0A buffer\_status<1>=0 TX buffer 1 can be filled by the MCU 0x0A buffer\_status<1>=1 TX buffer 1 should not be filled by the MCU 0x0A buffer\_status<0>=0 TX buffer 0 can be filled by the MCU 0x0A buffer\_status<0>=1 TX buffer 0 should not be filled by the MCU

## 7.3 Detailed Link Manager Protocol Description

### 7.3.1 Time Code

Time code is the time (in units of a known clock) after which the device that transmitted (or received) a data packet will transmit (or receive) again.

The data transmission is done in small bursts at high data rate which allows the devices to be active only a short period of time and therefore save power. In order to avoid collisions between different clients, different time code values can be used. The time code can be a fixed number, or taken randomly from the time code table in order to further decrease the possibility of collisions between different clients.

The client has a timer circuit running indicating the next communication time. The master has as many timers running in parallel as active clients. Each timer gives an interrupt when the appropriate client has to communicate with the master. The delay between the received RF signal and corresponding baseband signal (including the latency of any interrupts) is managed completely by the link manager.

Timers run using the 32.768 kHz XTAL or 6.25 kHz derived from the RCO.

The timer sizes of the different systems are presented in Table 7

Table 7. Timer Sizes

| Frequency  | Resolution           |

|------------|----------------------|

| 32.768 kHz | 1 / 32768Hz (~ 30µs) |

| 6.25kHz    | 1 / 6250Hz (~ 160µs) |

Clients can transmit data in intervals given in Table 8.

#### 7.3.1.1 Fixed time codes

Fixed time code values presented in Table 8 are hard-coded in a time code table. A programmable multiplier together with the time code number value selects which time code value is used.

The time code equals to time\_code\_scaling\*(895 + time\_code)/2048 s. For time\_code=FF, a time code is randomly taken with the selected time\_code\_scaling as described in Pseudo-random time code 7.3.1.2. The random time\_code is not supported during pairing and wakeup. For pairing and wakeup, the time\_code is set in register 0x93 PAIRWAKE\_TABLE\_3<7:0>. The time\_code\_scaling is set in register 0x92 PAIRWAKE\_TABLE\_4<5:4>. For data mode, the time\_code can be individually set for each client by the master in CLIENT\_n\_3<7:0> register. The time\_code\_scaling is set in CLIENT\_n\_0<4:3> register.

| Time code number | Time code value [s]     |                       |                       |                       |  |  |

|------------------|-------------------------|-----------------------|-----------------------|-----------------------|--|--|

|                  | time_code_scaling = 0.5 | time_code_scaling = 1 | time_code_scaling = 2 | time_code_scaling = 4 |  |  |

| 0                | 0.5 * 895 / 2048        | 1 * 895 / 2048        | 2 * 895 / 2048        | 4 * 895 / 2048        |  |  |

| 1                | 0.5* 896 / 2048         | 1* 896 / 2048         | 2 * 896 / 2048        | 4 * 896 / 2048        |  |  |

| 2                | 0.5* 897 / 2048         | 1* 897 / 2048         | 2 * 897 / 2048        | 4 * 897 / 2048        |  |  |

|                  |                         |                       |                       |                       |  |  |

| 126              | 0.5* 1021 / 2048        | 1* 1021 / 2048        | 2 * 1021 / 2048       | 4 * 1021 / 2048       |  |  |

| 127              | 0.5* 1022 / 2048        | 1* 1022 / 2048        | 2 * 1022 / 2048       | Reserved              |  |  |

|                  |                         |                       |                       |                       |  |  |

| 254              | 0.5* 1149 / 2048        | 1* 1149 / 2048        | 2 * 1149 / 2048       | Reserved              |  |  |

| 255              | 8-bit PRBS              | 8-bit PRBS            | 8-bit PRBS            | 7-bit PRBS            |  |  |

Note: If two clients use time code values that are close to each other and there is a collision, it takes long time until they get apart. It is recommended to select appropriate (ideally with largest possible difference) time code values so that the system can recover faster from collisions.

#### 7.3.1.2 Pseudo-random time code

A pseudo-random bit sequence (PRBS) generator is used to provide a pointer to the time code table in order to get the next time code value. The client and the master use the known seed (exchanged during wakeup or temporary pairing) for calculation of the next random time slot. In presence of disturbers or lost data packages, the next time slot is calculated independently.

For each active client a separate PRBS generator is running independently.

If the multiplier of 4 is used, a 7-bit PRBS value is used in order to be compatible with 16-bit timers. Otherwise, 8-bit PRBS value is used.

#### 7.3.2 Communication Mode

The communication mode defines the various combinations of modulation parameters (data rate and frequency deviation) in order to achieve the optimum RF performance. The supported communication modes are presented in Table 9.

| Communication Mode | Data Rate       | Frequency deviation | Channel spacing |

|--------------------|-----------------|---------------------|-----------------|

| 0                  | 250kbit/s       | 160 kHz             | 1MHz            |

| 1                  | 1Mbit/s         | 160 kHz             | 1MHz            |

| 2                  | 1Mbit/s 400 kHz |                     | 2MHz            |

| 3                  | 2Mbit/s         | 320 kHz             | 2MHz            |

| 4                  | 2Mbit/s         | 800 kHz             | 3MHz            |

| 5                  | Reserved        | Reserved            | Reserved        |

| 6                  | Reserved        | Reserved            | Reserved        |

| 7                  | Reserved        | Reserved            | Reserved        |

Table 9. Supported Communication Modes

**Note:** Channel spacing is only a recommendation for optimum behavior. Frequency channels can be selected with 1MHz resolution without any restrictions within the operation range.

#### 7.3.3 Frequency Channels

Channel frequencies from 2405MHz to 2480MHz supported.

#### 7.3.4 RSSI

The RSSI value indicates the level of the last correctly received packet (DATA, PAIR0/1, LMB, TEMP\_LMB, LIB, or MCDT\_RX). After the reception of the packet, the actual value LOG\_RSSI\_ACT\_VALUE<9:0> in address 0xB4 and 0xB5 is updated.

#### 7.3.4.1 RSSI Calibration

If a RSSI value of a certain input power level is needed, a reference measurement has to be done to calibrate the RSSI value. The RSSI calibration can be enabled by setting the RSSI alignment mode bit high (0b1) in register 0xE4. Known RF level (e.g. middle of dynamic range) must be applied to the antenna and the actual RSSI value in address 0xB4 and 0xB5 is measured. The MSB and LSB bits should be ignored and the remaining actual RSSI value bits [8:1] must be stored into the Device Data register in address 0xA6. The RSSI actual value is now aligned so that the reference level produces the value of 0b000000000.

#### 7.3.4.2 RSSI Accuracy

The automatic gain control (AGC) is setting the gain of the analog front-end with eight 6dB steps. The RSSI measurement can be accurately done only after the gain is settled. For accurate RSSI value, minimum payload length recommendation presented in Table 10 must be used. Four RSSI registers (one for each RX data buffer page) are accessible by the MCU via SDI.

Table 10. Minimum Payload Recommendations

| Data rate (kbps) | Minimum payload length (byte) |

|------------------|-------------------------------|

| 250              | -                             |

Table 10. Minimum Payload Recommendations

| Data rate (kbps) | Minimum payload length (byte) |

|------------------|-------------------------------|

| 1000             | 8                             |

| 2000             | 18                            |

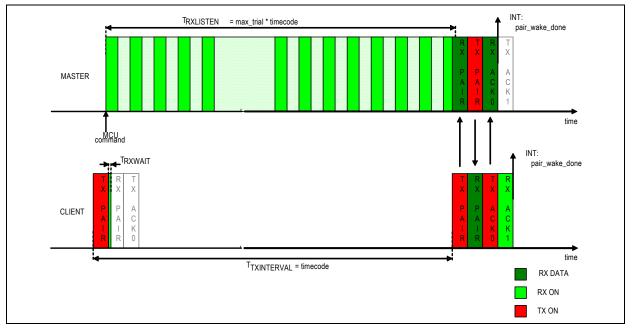

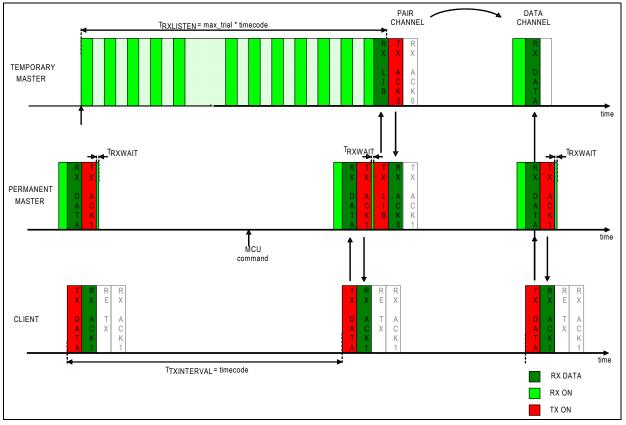

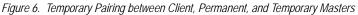

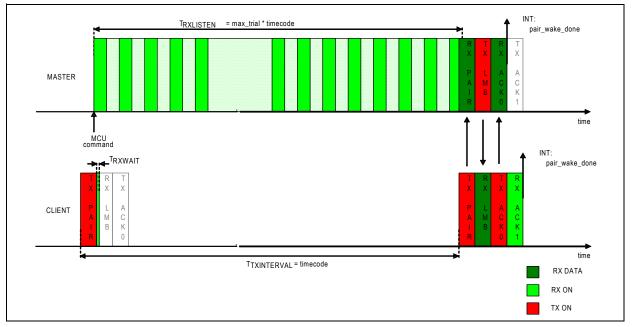

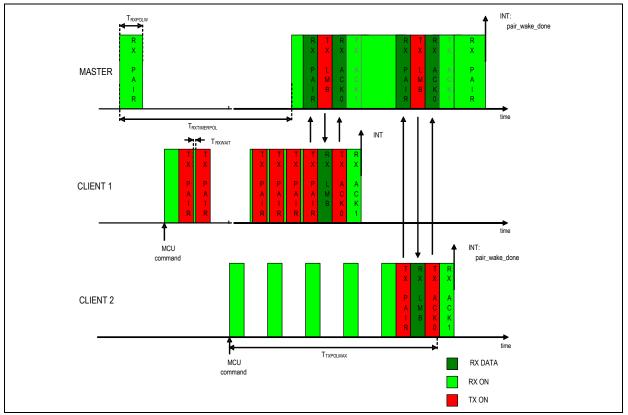

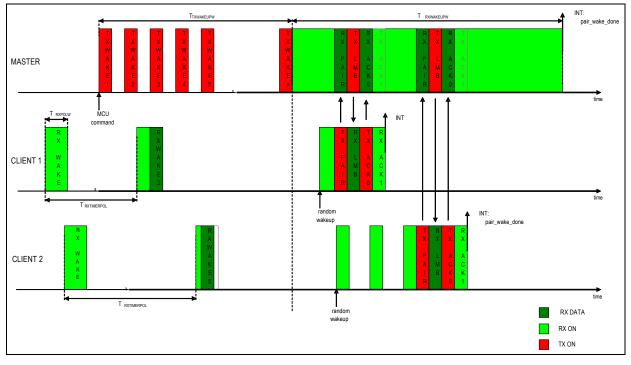

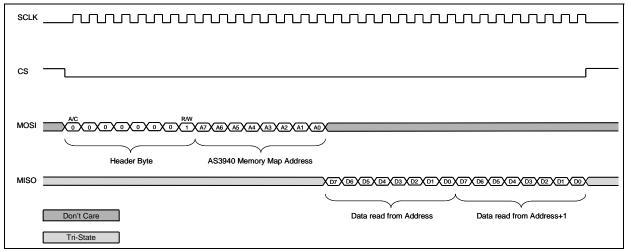

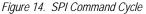

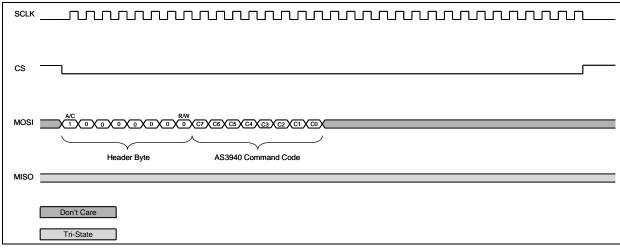

## 7.3.4.3 RSSI during pairing and LBT