# Wireless LAN Module MBH7WLZ16 Datasheet

Rev. 1.37e

Oct 2, 2009

# FUJITSU COMPONENT LIMITED

This product is designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but is not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

You shall not use this product for the above-mentioned uses.

If your equipment is likely to be used for the above-mentioned uses, please consult with our sales representative before use.

Fujitsu Component shall not be liable against you and/or any third party for any claims or damages arising in connection with the above-mentioned uses of this product.

All specifications are preliminary which may be changed without any prior notice

# 1. Introduction

This document applies to the Wireless LAN module MBH7WLZ16.

# 2. Features

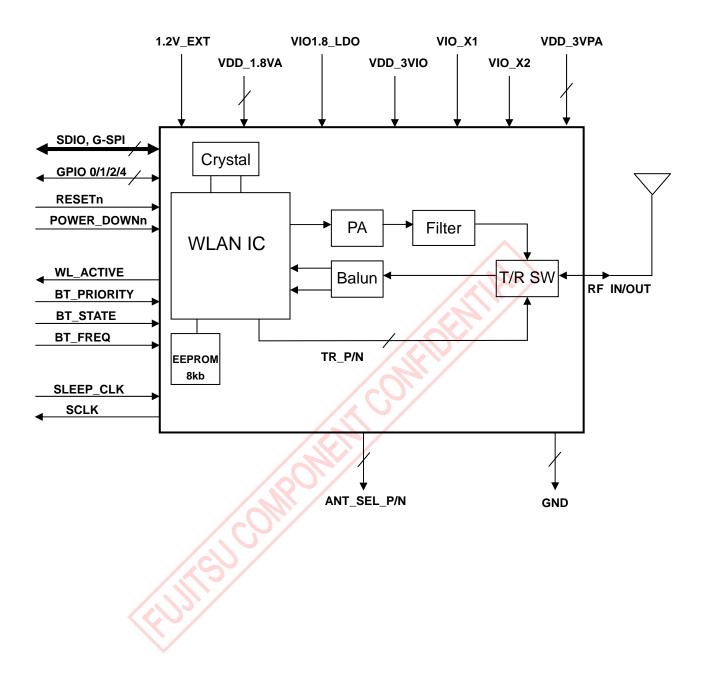

MBH7WLZ16 is a microminiaturized Wireless LAN module conforming to the IEEE standard 802.11/802.11b/ 802.11g, and transmits and receives in the 2.4 GHz ISM band. MBH7WLZ16 has the following features:

- IEEE standard 802.11/802.11b/802.11g Compliant

- Frequency Range: 2400 2497 MHz

- (1 13 channel (IEEE802.11/11b/11g), 14 channel (IEEE802.11/11b) ISM band)

- Modulation Technique: Direct Sequence Spread Spectrum (CCK, DQPSK, DBPSK)

Orthogonal Frequency Division Multiplexing (64QAM, 16QAM, DQPSK, DBPSK)

- Transmission Rate: 1 Mbps, 2 Mbps (802.11), 5.5 Mbps, 11 Mbps (802.11b)

- 6 Mbps, 9 Mbps, 12 Mbps, 18 Mbps, 24 Mbps, 36 Mbps, 48 Mbps, 54 Mbps (802.11g)

- Host Interface: SDIO

- Generic SPI (G-SPI)

- Security: 64/128-bit WEP, WPA (TKIP), WPA2 (AES-CCMP)

507

- QoS (Quality of Service) support

- Bluetooth Coexistence support

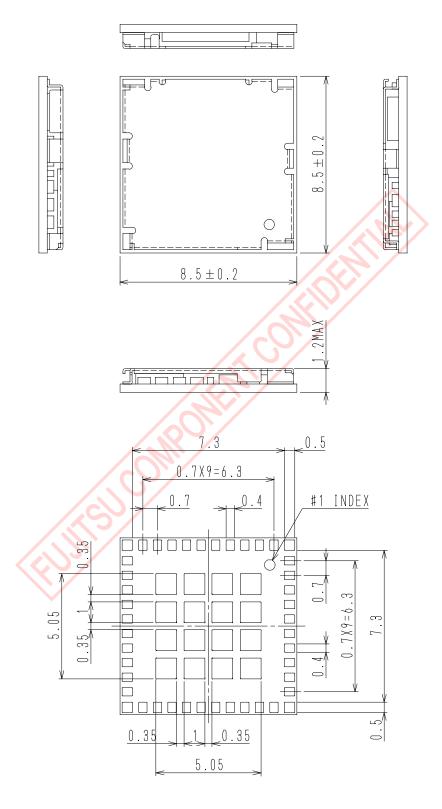

- Surface mount, 60pin LGA type (Compatible with Pb-free solder processing)

- RoHS Compliant

- Miniaturized package: 8.5 x 8.5 x 1.2 mm

- Antenna port: Single Antenna port

- Built-in Crystal Oscillator

- Low power consumption

# 4. Pin Description and Power

# 4-1. Pin Description

| Name                 | No.   | I/O | Description                                                                                                                  |  |  |  |

|----------------------|-------|-----|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SPI_SDI/             | 18    | I/O | G-SPI mode: G-SPI Data Input                                                                                                 |  |  |  |

| SD_CMD               |       |     | SDIO 4-bit mode: Command/Response                                                                                            |  |  |  |

|                      |       |     | SDIO 1-bit mode: Command Line                                                                                                |  |  |  |

|                      |       |     | SDIO SPI mode: Data Input                                                                                                    |  |  |  |

| SPI_CLK/             | 19    | I/O | G-SPI mode: G-SPI Clock Input                                                                                                |  |  |  |

| SD_CLK               |       |     | SDIO 4-bit mode: Clock Input                                                                                                 |  |  |  |

|                      |       |     | SDIO 1-bit mode: Clock Input                                                                                                 |  |  |  |

|                      | 17    |     | SDIO SPI mode: Clock Input                                                                                                   |  |  |  |

| SPI_SCSn/<br>SD_DAT0 | 17    | I/O | G-SPI mode: G-SPI Chip Select Input (active low)                                                                             |  |  |  |

| SD_DATU              |       |     | SDIO 4-bit mode: Data Line Bit [0]<br>SDIO 1-bit mode: Data Line                                                             |  |  |  |

|                      |       |     | SDIO FDICINOUE. Data Line<br>SDIO SPI mode: Data Output                                                                      |  |  |  |

| SPI SDO/             | 16    | I/O | G-SPI mode: G-SPI Data Output                                                                                                |  |  |  |

| SD DAT1              | 10    | 1/0 | SDIO 4-bit mode: Data Line Bit [1]                                                                                           |  |  |  |

| 00_0/11              |       |     | SDIO 1-bit mode: Interrupt                                                                                                   |  |  |  |

|                      |       |     | SDIO SPI mode: Reserved                                                                                                      |  |  |  |

| SPI_SINTn/           | 15    | I/O | G-SPI mode: G-SPI Interrupt Output (active low)                                                                              |  |  |  |

| SD_DAT2              | -     |     | SDIO 4-bit mode: Data Line Bit [2] or Read Wait (optional)                                                                   |  |  |  |

|                      |       |     | SDIO 1-bit mode: Read Wait (optional)                                                                                        |  |  |  |

|                      |       |     | SDIO SPI mode: Reserved                                                                                                      |  |  |  |

| SD_DAT3              | 14    | I/O | SDIO 4-bit mode: Data Line Bit [3]                                                                                           |  |  |  |

|                      |       |     | SDIO 1-bit mode: Reserved                                                                                                    |  |  |  |

|                      |       |     | SDIO SPI mode: Card Select (active low)                                                                                      |  |  |  |

| GPIO[0]/             | 11    | I/O | General Purpose Input/Output (Internal pull-up)                                                                              |  |  |  |

| SLEEPn               |       |     | These pins are asynchronous to internal clocks. Several of these pins can be                                                 |  |  |  |

| GPIO[1]/             | 21    | I/O | selected to perform alternate functions such as an LED controller.                                                           |  |  |  |

| LED                  |       |     | When not used, these pins should be left floating.                                                                           |  |  |  |

| GPIO[2]              | 39    | I/O | Notes:                                                                                                                       |  |  |  |

|                      |       |     | GPIO[0]: SLEEPn. This pin drives low during power down sleep mode.                                                           |  |  |  |

| GPIO[4]/             | 20    | I/O | GPIO[1]: LED output (strap pin). Transmit power or receive ready LED.                                                        |  |  |  |

| Module_wake_up       |       |     | GPIO[4]: WLAN MAC wake-up input / Interrupt input                                                                            |  |  |  |

| WL_ACTIVE            | 40    | 0   | Bluetooth WLAN Active                                                                                                        |  |  |  |

|                      |       |     | 2-Wire BCA Mode:                                                                                                             |  |  |  |

|                      |       |     | When high, WLAN is transmitting or receiving packets.<br><b>3-Wire BCA Mode:</b>                                             |  |  |  |

|                      |       |     | 0 = Bluetooth device allowed to transmit                                                                                     |  |  |  |

|                      |       |     | 1 = Bluetooth device allowed to transmit                                                                                     |  |  |  |

|                      |       |     | This pin drives low when POWER_DOWNn is asserted.                                                                            |  |  |  |

|                      |       |     | In WLAN Sleep mode, all I/O PADs are powered down. This pad must stay at a low                                               |  |  |  |

|                      |       |     | state even in power down mode.                                                                                               |  |  |  |

| BT_PRIORITY          | 42    |     | Bluetooth Priority                                                                                                           |  |  |  |

|                      |       |     | 2-Wire BCA Mode:                                                                                                             |  |  |  |

|                      |       |     | When high, Bluetooth is transmitting or receiving high priority packets.                                                     |  |  |  |

|                      | ( ) ) |     | 3-Wire BCA Mode:                                                                                                             |  |  |  |

|                      |       |     | When high, Bluetooth is transmitting or receiving packets.                                                                   |  |  |  |

| BT_STATE             | 41    | Ι   | Bluetooth State                                                                                                              |  |  |  |

|                      |       |     | 0 = normal priority, Rx                                                                                                      |  |  |  |

|                      |       |     | 1 = high priority, Tx                                                                                                        |  |  |  |

|                      |       |     | Priority is signaled after BT_PRIORITY has been asserted. After priority signaling,                                          |  |  |  |

|                      | 40    |     | BT_STATE indicates the Tx/Rx mode of Bluetooth radio.                                                                        |  |  |  |

| BT_FREQ              | 43    | I   | 4-Wire BCA Mode:                                                                                                             |  |  |  |

|                      |       |     | Bluetooth Frequency                                                                                                          |  |  |  |

|                      |       |     | Asserted (logic high) when the Bluetooth transceiver hops into the restricted channels defined by the coexistence mechanism. |  |  |  |

|                      |       |     | 2-Wire, 3-Wire BCA Mode:                                                                                                     |  |  |  |

|                      |       |     | Tied to ground (GND)                                                                                                         |  |  |  |

| ANT_SEL_P            | 37    | 0   | Differential Antenna Select Positive Output                                                                                  |  |  |  |

|                      | 01    | 0   | Provides the antenna select positive control signal.                                                                         |  |  |  |

|                      |       |     | Default value is 1.                                                                                                          |  |  |  |

|                      |       |     | Also used as RF switch control for single Bluetooth/WLAN antenna configurations.                                             |  |  |  |

|                      |       |     | ANT_SEL_N ANT_SEL_P For antenna For single                                                                                   |  |  |  |

|                      |       |     | diversity BT/WLAN antenna                                                                                                    |  |  |  |

|                      |       |     | 0 0                                                                                                                          |  |  |  |

|                      |       |     | 0 1 Antenna 1 Bluetooth                                                                                                      |  |  |  |

|                      |       |     | 1 0 Antenna 0 WLAN                                                                                                           |  |  |  |

|                      |       |     | 1 1                                                                                                                          |  |  |  |

|                      | 1     |     |                                                                                                                              |  |  |  |

| ANT SEL N   | 36           | 0      | Differential Anter                                                     | nna Select Nega    | tive Output          |                               |  |  |

|-------------|--------------|--------|------------------------------------------------------------------------|--------------------|----------------------|-------------------------------|--|--|

|             |              | -      |                                                                        |                    | ative control signal |                               |  |  |

|             |              |        | Default value is                                                       |                    | <b>j</b>             |                               |  |  |

|             |              |        | Also used as RF                                                        | switch control f   | or single Bluetooth  | WLAN antenna configurations   |  |  |

|             |              |        | ANT_SEL_N                                                              | ANT_SEL_P          | For antenna          | For single                    |  |  |

|             |              |        |                                                                        |                    | diversity            | BT/WLAN antenna               |  |  |

|             |              |        | 0                                                                      | 0                  |                      |                               |  |  |

|             |              |        | 0                                                                      | 1                  | Antenna 1            | Bluetooth                     |  |  |

|             |              |        | 1                                                                      | 0                  | Antenna 0            | WLAN                          |  |  |

|             |              |        | 1                                                                      | 1                  |                      |                               |  |  |

| RESETn      | 8            | I      | Reset (active low                                                      | v, Internal pull-u | o)                   |                               |  |  |

| POWER_DOWNn | 7            | I      | Full power down                                                        | (active low, Inte  | rnal pull-up)        |                               |  |  |

|             |              |        | 0 = full power do                                                      |                    |                      |                               |  |  |

|             |              |        | 1 = normal mode                                                        | -                  |                      |                               |  |  |

|             |              |        | Connect to powe                                                        |                    |                      |                               |  |  |

| SLEEP_CLK   | 9            | I      | Clock Input for E                                                      |                    |                      |                               |  |  |

|             |              |        | NOTE: SLEEP_CLK is used by the WLAN and Bluetooth MAC. The input clock |                    |                      |                               |  |  |

|             |              |        |                                                                        |                    |                      | The Bluetooth radio chip sup  |  |  |

| 0011/       |              |        | 3.2 kHz. The WL                                                        |                    |                      |                               |  |  |

| SCLK        | 24           | 0      | Serial Interface                                                       |                    |                      | nt dovice programming interfe |  |  |

|             |              |        | control.                                                               | CIOCK OUTPUT FOR   | power manageme       | nt device programming interfa |  |  |

| RF IN/OUT   | 3            | RF     | Antenna port, 50                                                       | 0                  |                      |                               |  |  |

| 1.2V EXT    | 22           | Power  | 1.2V Digital Pow                                                       |                    |                      |                               |  |  |

| VDD 1.8VA 1 | 5            | Power  | 1.8V Analog Pov                                                        |                    |                      |                               |  |  |

| VDD_1.8VA_1 | 6            | Power  | 1.8V Analog Pov                                                        |                    |                      |                               |  |  |

| VIO1.8 LDO  | 29           | Power  |                                                                        |                    | age Regulator Pow    | ver Supply                    |  |  |

| VDD_3VIO    | 27           | Power  | 3.0V Digital I/O                                                       |                    | age regulater f en   |                               |  |  |

| VIO X1      | 13           | Power  | 1.8V/3.3V Host \$                                                      |                    |                      |                               |  |  |

| VIO X2      | 26           | Power  | 1.8V/3.3V Digita                                                       |                    |                      |                               |  |  |

| VDD 3VPA 1  | 32           | Power  | 3.0V Power Sup                                                         |                    |                      |                               |  |  |

| VDD 3VPA 2  | 31           | Power  | 3.0V Power Sup                                                         |                    |                      |                               |  |  |

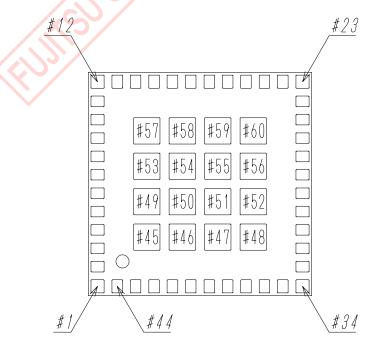

| GND         | 1,2,4,10,    | Ground | Ground                                                                 |                    |                      |                               |  |  |

|             | 12,23,25,28, |        |                                                                        |                    |                      |                               |  |  |

|             | 30,33,34,35  |        |                                                                        |                    |                      |                               |  |  |

|             | 38,44,45,46, |        |                                                                        |                    |                      |                               |  |  |

|             | 47,48,49,50, |        |                                                                        |                    |                      |                               |  |  |

|             | 51,52,53,54, |        |                                                                        |                    |                      |                               |  |  |

|             | 55,56,57,58, |        | V                                                                      |                    |                      |                               |  |  |

|             | 59,60        |        |                                                                        |                    |                      |                               |  |  |

I/O Type:

I: Digital Input,

O: Digital Output,

I/O: Digital Input/Output

Pin Assignment (Bottom View)

Confidential Copyright © FUJITSU COMPONENT LIMITED 2006-2009 - 4 -

MBH7WLZ16 requires the following supply voltages:

- 1.2V\_EXT 1.2V Digital Core Power Supply (1.2V Supply can be derived from the Internal Voltage Regulator.)

- VDD\_1.8VA\_1, VDD\_1.8VA\_2 1.8V Analog Power Supply

- VIO1.8\_LDO 1.8V Digital I/O and Internal Voltage Regulator Power Supply

- VIO\_X1 1.8V/3.3V Host Power Supply

- VIO\_X2 1.8V/3.3V Digital Power Supply

- VDD\_3VIO 3.0V Digital I/O Power Supply

- VDD\_3VPA\_1, VDD\_3VPA\_2 3.0V PA Power Supply

The following table lists the pins operating from each voltage supply.

| No. | Name                   | No.  | Name   | No. | Name      | No.  | Name        |

|-----|------------------------|------|--------|-----|-----------|------|-------------|

| VIO | _X1                    | VIO_ |        | VDD | _3VIO     | VIO1 | .8_LDO      |

|     | POWER_DOWNn            | 24   | SCLK   | 36  | ANT_SEL_N |      | WL_ACTIVE   |

|     | RESETn                 |      |        | 37  | ANT_SEL_P | 41   | BT_STATE    |

|     | SLEEP_CLK              |      |        |     |           |      | BT_PRIORITY |

|     | GPIO[0]/SLEEPn         |      |        |     |           | 43   | BT_FREQ     |

| 14  | SD_DAT3                |      |        |     |           |      |             |

|     | SPI_SINTn/SD_DAT2      |      |        |     |           |      |             |

| 16  | SPI_SDO/SD_DAT1        |      |        |     |           |      |             |

|     | SPI_SCSn/SD_DAT0       |      |        |     |           |      |             |

|     | SPI_SDI/SD_CMD         |      |        |     |           |      |             |

|     | SPI_CLK/SD_CLK         |      |        |     |           |      |             |

|     | GPIO[4]/Module_wake_up |      |        | 10  |           |      |             |

|     | GPIO[1]/LED            |      |        |     | <u> </u>  |      |             |

| 39  | GPIO[2]                |      |        |     |           |      |             |

|     | FUI                    |      | SOMPON |     |           |      |             |

|     |                        |      |        |     |           |      |             |

# 5. Electrical Characteristics

# 5-1. General Specification

| Network Standard      | IEEE standard 802.11/802.11b/802.11g Compliant                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interface             | Secure Digital Input/Output (SDIO)<br>Generic SPI (G-SPI)                                                                                                                             |

| Frequency Band        | 2400 ~ 2497 MHz (ISM band)<br>(IEEE802.11b: Channel 1 ~ 14, IEEE802.11g: Channel 1 ~ 13)                                                                                              |

| Data Transfer Mode    | Direct Sequence Spread Spectrum (DSSS)<br>Orthogonal Frequency Division Multiplexing (OFDM)                                                                                           |

| Modulation Techniques | CCK (11 Mbps, 5.5 Mbps), DQPSK (2 Mbps), DBPSK (1 Mbps)<br>OFDM-64QAM (54 Mbps, 48 Mbps), OFDM-16QAM (36 Mbps, 24 Mbps)<br>OFDM-DQPSK (18 Mbps, 12 Mbps), OFDM-DBPSK (9 Mbps, 6 Mbps) |

| Media Access Protocol | CSMA/CA (Carrier Sense Multiple Access with Collision Avoidance)                                                                                                                      |

| Access Method         | Ad-Hoc mode, Infrastructure mode                                                                                                                                                      |

| Absolute Maximum Rat  | ing                                                                                                                                                                                   |

# 5-2. Absolute Maximum Rating

| Symbol                      | Parameter                                | Min | Тур | Max  | Unit     |

|-----------------------------|------------------------------------------|-----|-----|------|----------|

| 1.2V_EXT                    | Power Supply Voltage with respect to GND |     | 1.2 | 1.35 | V        |

| VDD_1.8VA_1,<br>VDD_1.8VA_2 | Power Supply Voltage with respect to GND |     | 1.8 | 2.3  | V        |

| VIO1.8_LDO                  | Power Supply Voltage with respect to GND |     | 1.8 | 2.3  | V        |

| VDD_3VIO                    | Power Supply Voltage with respect to GND |     | 3.0 | 3.5  | V        |

| VIO X1                      | Bower Supply Veltage with respect to CND |     | 1.8 | 2.3  | V        |

|                             | Power Supply Voltage with respect to GND |     | 3.3 | 4.2  | V        |

| VIO X2                      | Power Supply Veltage with respect to GND |     | 1.8 | 2.3  | V        |

| VIO_72                      | Power Supply Voltage with respect to GND |     | 3.3 | 4.2  | V        |

| VDD_3VPA_1,<br>VDD_3VPA_2   | Power Supply Voltage with respect to GND |     | 3.3 | 5.0  | V        |

| T <sub>STORAGE</sub>        | Storage Temperature                      | -40 | +25 | +105 | °C       |

| T <sub>STORAGE</sub>        | Storage Temperature                      | -40 | 4   | -25  | -25 +105 |

# 5-3. Recommendable Operating Condition

| Symbol                      | Parameter                                    | Min  | Тур | Max  | Unit |

|-----------------------------|----------------------------------------------|------|-----|------|------|

| 1.2V_EXT                    | 1.2V digital power supply                    | 1.08 | 1.2 | 1.32 | V    |

| VDD_1.8VA_1,<br>VDD_1.8VA_2 | 1.8V analog I/O power supply                 | 1.7  | 1.8 | 1.9  | V    |

| VIO1.8_LDO                  | 1.8V internal voltage regulator power supply | 1.62 | 1.8 | 1.98 | V    |

| VDD_3VIO                    | 3.0V digital I/O power supply                | 2.95 | 3.0 | 3.3  | V    |

| VIO X1                      | Host interface digital I/O power supply      | 1.62 | 1.8 | 1.98 | V    |

|                             | Host interface digital I/O power supply      | 2.97 | 3.3 | 3.63 | V    |

| VIO X2                      | 1.8V digital I/O power supply                | 1.62 | 1.8 | 1.98 | V    |

| VIO_72                      | 1.0 V digital 1/O power suppry               | 2.97 | 3.3 | 3.63 | V    |

| VDD_3VPA_1,<br>VDD_3VPA_2   | 3.0V PA power supply                         | 3.0  | 3.3 | 3.6  | V    |

| T <sub>A</sub>              | Ambient operating temperature                | -20  | +25 | +70  | °C   |

# 5-4. DC Electricals – Digital 3V Pads (VDD\_3VIO)

| Symbol           | Parameter                       | Min  | Тур | Max                  | Unit |

|------------------|---------------------------------|------|-----|----------------------|------|

| V <sub>30</sub>  | Power supply voltage (VDD_3VIO) | 2.95 | 3.0 | 3.3                  | V    |

| VIH              | Input high voltage              | 2.0  |     | V <sub>30</sub> +0.3 | V    |

| VIL              | Input low voltage               | -0.3 |     | 0.6                  | V    |

| V <sub>HYS</sub> | Input hysteresis                | 250  |     |                      | mV   |

| V <sub>OH</sub>  | Output high voltage             | 2.3  |     |                      | V    |

| V <sub>OL</sub>  | Output low voltage              |      |     | 0.4                  | V    |

# 5-5. DC Electricals – Digital 1.8V/3V Pads (VIO\_X1, VIO\_X2)

| Symbol                | Parameter                                | Mode | Condition                                                                                                                                                                                          | Min  | Тур | Max                  | Unit |

|-----------------------|------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----------------------|------|

| V <sub>18</sub>       | Power supply voltage (VIO_X1, VIO_X2)    | 1.8V |                                                                                                                                                                                                    | 1.62 | 1.8 | 1.98                 | V    |

| V <sub>33</sub>       | Power supply voltage<br>(VIO_X1, VIO_X2) | 3.3V |                                                                                                                                                                                                    | 2.97 | 3.3 | 3.63                 | V    |

| V <sub>IH</sub>       | Input high voltage                       | 1.8V |                                                                                                                                                                                                    | 1.2  | /   | V <sub>18</sub> +0.3 | V    |

|                       |                                          | 3.3V |                                                                                                                                                                                                    | 2.0  |     | V <sub>33</sub> +0.3 | V    |

| V <sub>IL</sub>       | Input low voltage                        | 1.8V |                                                                                                                                                                                                    | -0.3 |     | 0.6                  | V    |

|                       |                                          | 3.3V |                                                                                                                                                                                                    | -0.3 |     | 1                    |      |

| V <sub>HYS</sub>      | Input hysteresis                         | 1.8V |                                                                                                                                                                                                    | 250  |     |                      | mV   |

|                       |                                          | 3.3V |                                                                                                                                                                                                    | 300  |     |                      | mV   |

| V <sub>OH</sub>       | Output high voltage                      | 1.8V | $SR^1 = Slew Rate^2$                                                                                                                                                                               | 1.22 |     |                      | V    |

|                       |                                          |      | SR      I <sub>OH</sub> (max)        3      16 mA        2      16 mA        1      5 mA        0      5 mA                                                                                        |      |     |                      |      |

|                       | OMP                                      | 3.3V | $\begin{array}{c c} SR = Slew Rate \\ \hline SR & I_{OH}(max) \\ \hline 3 & 16.5 \text{ mA} \\ \hline 2 & 16.5 \text{ mA} \\ \hline 1 & 5.5 \text{ mA} \\ \hline 0 & 5.5 \text{ mA} \end{array}$   | 2.57 |     |                      | V    |

| V <sub>OL</sub>       | Output low voltage                       | 1.8V | $\begin{array}{c c} SR = Slew Rate^{3} \\ \hline SR & I_{0L}(max) \\ \hline 3 & 23 \text{ mA} \\ \hline 2 & 15.5 \text{ mA} \\ \hline 1 & 7.5 \text{ mA} \\ \hline 0 & 7.5 \text{ mA} \end{array}$ |      |     | 0.4                  | V    |

|                       |                                          | 3.3V | SR = Slew Rate        SR      IoL(max)        3      23.5 mA        2      15.5 mA        1      7.5 mA        0      7.5 mA                                                                       |      |     | 0.4                  | V    |

| I_pullup <sup>4</sup> |                                          |      |                                                                                                                                                                                                    | 16   | 22  | 29                   | μA   |

| I_pulldown            |                                          |      |                                                                                                                                                                                                    | 12   | 23  | 33                   | μA   |

| <br>I_pullup_weak     |                                          |      |                                                                                                                                                                                                    |      |     | 10                   | μA   |

| I_pulldown_wea        | ak                                       |      |                                                                                                                                                                                                    |      |     | 10                   | μA   |

1. Slew rate that controls the output drive strength and rise/fall time of the pad.

2.  $I_{\text{OH}}$  is the maximum current draw to maintain a minimum  $V_{\text{OH}}$  level.

3.  $I_{\text{OL}}$  is the maximum sink current to maintain a maximum  $V_{\text{OL}}$  level.

4. There are two types of pull-up/pull-down pads—regular and weak. Each pad type (regular and weak) has different internal resistor values.

# 5-6. Power Supply Configurations

For flexibility, MBH7WLZ16 integrates an internal voltage regulator. The 1.2V\_EXT supply can be derived from this regulator.

The following table lists the connections of the VIO1.8\_LDO and 1.2V\_EXT power supplies in various applications.

| Configuration                                                              | VIO1.8_LDO | 1.2V_EXT      |

|----------------------------------------------------------------------------|------------|---------------|

| Internal voltage regulator with/without<br>Bluetooth coexistence interface | Connected  | Not Connected |

| External 1.2V supply with/without<br>Bluetooth coexistence interface       | Connected  | Connected     |

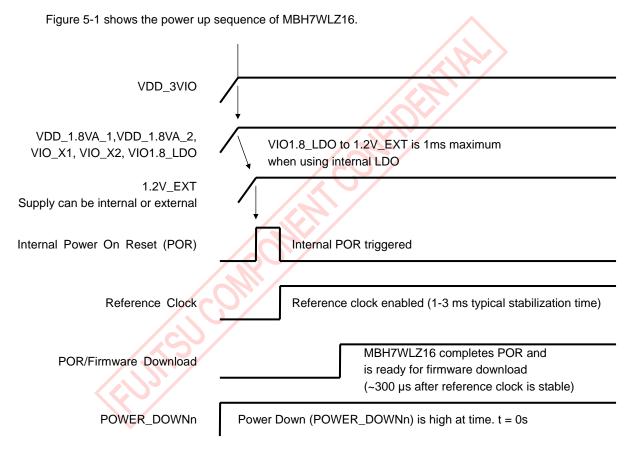

### 5-7. Power Sequence

Figure 5-1 Power Up Timing Sequence

#### 5-8. Power Management

The following table lists the state of the functional pins when in power down mode.

| No. | Tri-State (Floating)   | No. | Output Low     | No. | Output High |

|-----|------------------------|-----|----------------|-----|-------------|

| 9   | SLEEP_CLK              | 11  | GPIO[0]/SLEEPn | 37  | ANT_SEL_P   |

| 14  | SD_DAT3                | 24  | SCLK           |     |             |

| 15  | SPI_SINTn/SD_DAT2      | 36  | ANT_SEL_N      |     |             |

| 16  | SPI_SDO/SD_DAT1        | 39  | GPIO[2]        |     |             |

| 17  | SPI_SCSn/SD_DAT0       | 40  | WL_ACTIVE      |     |             |

| 18  | SPI_SDI/SD_CMD         |     |                |     |             |

| 19  | SPI_CLK/SD_CLK         |     |                |     |             |

| 20  | GPIO[4]/Module_wake_up |     |                |     |             |

| 21  | GPIO[1]/LED            |     |                |     |             |

| 41  | BT_STATE               |     |                |     |             |

| 42  | BT_PRIORITY            |     |                |     |             |

| 43  | BT_FREQ                |     |                |     |             |

#### 5-9. Reset Configuration

MBH7WLZ16 is reset to its default operating state under the following conditions:

- Power-on reset

- Software/Firmware reset

# 5-9-1. Internal Reset

MBH7WLZ16 is reset and the internal CPU begins the boot sequence when any of the following internal reset events occurs:

- MBH7WLZ16 receives power and the 1.2V supply rises (this triggers the internal POR circuit)

- Internal CPU issues a software reset

- Host driver issues a soft reset

- Watchdog timer expires (used for debug purpose only)

### 5-9-2. External Reset

MBH7WLZ16 is reset and the internal CPU begins the boot sequence when the RESETn input pin transitions from low to high.

#### 5-9-3. Calibration

MBH7WLZ16 performs calibration when the device is powered up. In addition, calibration is also performed under the following operating conditions:

- Exiting receive mode

- Exiting transmit mode

- Change of channel frequency

# 5-10. RF Specification\*<sup>1</sup>

| ltems                                    |               | Condition                        | Min | Тур  | Max | Unit  |

|------------------------------------------|---------------|----------------------------------|-----|------|-----|-------|

|                                          |               | 54 Mbps (64QAM)                  |     | 12.0 |     | dBm   |

|                                          |               | 48 Mbps (64QAM)                  | -   | 12.0 | -   | UDIII |

|                                          |               | 36 Mbps (16QAM)                  |     |      |     |       |

|                                          |               | 24 Mbps (16QAM)                  |     |      |     |       |

|                                          |               | 18 Mbps (DQPSK)                  | _   | 15.0 | _   | dBm   |

|                                          | Channel 1-13  | 12 Mbps (DQPSK)                  | _   | 10.0 | _   | ubm   |

|                                          |               | 9 Mbps (DBPSK)                   |     |      |     |       |

| Transmit power levels                    |               | 6 Mbps (DBPSK)                   |     |      |     |       |

| ·                                        |               | 11 Mbps (CCK)                    |     |      |     |       |

|                                          |               | 5.5Mbps (CCK)                    | -   | 16.0 | -   | dBm   |

|                                          |               | 2 Mbps (DQPSK)                   |     |      |     |       |

|                                          |               | 1 Mbps (DBPSK)                   |     |      |     |       |

|                                          |               | 11 Mbps (CCK)                    |     |      | -   |       |

|                                          | Channel 14    | 5.5Mbps (CCK)                    | -   | 8.0  |     | dBm   |

|                                          |               | 2 Mbps (DQPSK)<br>1 Mbps (DBPSK) |     | ~    |     |       |

| 802.11b                                  | 1st Side Lobe |                                  | -   | -    | -30 | dBr   |

| Transmit spectrum mask                   | 2nd Side Lobe | 1 Mbps (DBPSK)                   |     |      | -50 | dBr   |

| •                                        | 11 MHz offset |                                  |     | _    | -20 | dBr   |

| 802.11g                                  | 20 MHz offset | 6 Mbps (DBPSK)                   |     | -    | -28 | dBr   |

| Transmit spectrum mask                   | 30 MHz offset |                                  |     | -    | -40 | dBr   |

| Transmit center frequency                |               | 54 Mbps (64QAM)                  | -25 | -    | 25  | ppm   |

| Symbol clock frequency tol               | erance        | 54 Mbps (64QAM)                  | -25 | -    | 25  | ppm   |

| Transmit power-on ramp                   |               | 11 Mbps (CCK)                    | -   | -    | 2   | μs    |

| Transmit power-down ramp                 | )             | 11 Mbps (CCK)                    | -   | -    | 2   | μs    |

| RF carrier suppression                   |               | 2 Mbps (DQPSK)                   | 15  | -    | -   | dB    |

| EVM (Peak)                               |               | 11 Mbps (CCK)                    | -   | 10   | 35  | %     |

|                                          |               | 1 Mbps (DBPSK)                   | -   | 8    | 35  | %     |

| EVM (RMS)                                |               | 54 Mbps (64QAM)                  | -   | -31  | -25 | dB    |

| 2 (1 )                                   |               | 6 Mbps (DBPSK)                   | -   | -28  | -5  | dB    |

|                                          |               | 54 Mbps (64QAM)                  | -   | -74  | -65 | dBm   |

| Receiver minimum input level sensitivity |               | 6 Mbps (DBPSK)                   | -   | -90  | -82 | dBm   |

|                                          |               | 11 Mbps (CCK)                    | -   | -89  | -76 | dBm   |

|                                          |               | 1 Mbps (DBPSK)                   | -   | -92  | -85 | dBm   |

| Receiver maximum input le                | evel          | 54 Mbps (64QAM)                  | -20 | -    | -   | dBm   |

|                                          |               | 11 Mbps (CCK)                    | -10 | -    | -   | dBm   |

| Receiver adjacent channel                | rejection     | 54 Mbps (64QAM)                  | -1  | -    | -   | dB    |

|                                          |               | 11 Mbps (CCK)                    | 35  | -    | -   | dB    |

\*1) Over full range of values specified in the Recommended Operating Conditions unless otherwise specified.

# 6. Host Interface

MBH7WLZ16 connects several host interface bus units to the internal bus of the device. The connection of each host interface bus unit to the internal bus is multiplexed with the other host interface bus units. MBH7WLZ16 allows only one host interface unit to be active at a time.

MBH7WLZ16 supports the following host interfaces:

- SDIO interface

- G-SPI interface

#### 6-1. SDIO Interface

MBH7WLZ16 supports a SDIO device interface that conforms to the industry standard SDIO Full-Speed card specification and allows a host controller using the SDIO bus protocol to access the WLAN device. The SDIO interface contains interface circuitry between an external SDIO bus and the internal shared bus.

MBH7WLZ16 acts as the device on the SDIO bus. The host unit can access registers of the SDIO interface directly and can access shared memory in MBH7WLZ16 through the use of BARs and a DMA engine.

The SDIO device interface main features include:

- Internal memory used for CIS

- Supports SPI, 1-bit SDIO, and 4-bit SDIO transfer mode at the full clock range of 0 to 50 MHz

- Special Interrupt register for information exchange

- Allows module to interrupt host

The SDIO interface pins are powered from the VIO\_X1 voltage supply.

#### 6-1-1. SDIO Command List

All mandatory SDIO commands are supported for both SDIO and SPI modes. SDIO mode commands are shown in Table 6-1. SPI mode commands are shown in Table 6-2.

| Command | Command Name         | Description                                                 |  |  |  |  |

|---------|----------------------|-------------------------------------------------------------|--|--|--|--|

| CMD0    | GO_IDLE_STATE        | Used to change from SDIO to SPI mode                        |  |  |  |  |

| CMD3    | SEND_RELATIVE_ADDR   | SDIO Host asks for RCA                                      |  |  |  |  |

| CMD5    | IO_SEND_OP_COND      | SDIO Host asks for and sets operation voltage               |  |  |  |  |

| CMD7    | SELECT/DESELECT_CARD | Sets SDIO target device to command state or back to standby |  |  |  |  |

| CMD15   | GO_INACTIVE_STATE    | Sets SDIO target device to inactive state                   |  |  |  |  |

| CMD52   | IO_RW_DIRECT         | Used to read/write host register and CIS table              |  |  |  |  |

| CMD53   | IO_RW_EXTENDED       | Used to read/write data from/to SQU memory                  |  |  |  |  |

Table 6-1 SDIO Mode, SDIO Commands

| Table 6-2 | SPI Mode, SDIO Commands |

|-----------|-------------------------|

|-----------|-------------------------|

| Command | Command Name    | Description                                    |

|---------|-----------------|------------------------------------------------|

| CMD0    | GO_IDLE_STATE   | Used to change from SDIO to SPI mode           |

| CMD5    | IO_SEND_OP_COND | Used in initialization state                   |

| CMD52   | IO_RW_DIRECT    | Used to read/write host register and CIS table |

| CMD53   | IO_RW_EXTENDED  | Used to read/write data from/to SQU memory     |

| CMD58   | CRC_ON_OFF      | SPI only. Enable/disable CRC                   |

#### 6-1-2. Power-Up Initialization

The power-up transaction sequences for SDIO and SPI modes are as follows:

# 6-1-2-1. SDIO Mode Power-Up Transaction Sequence

- (1) CMD5 (arg = 0)

- (2) SDIO Card response with OCR

- (3) CMD5 from host to set operation voltage using OCR

- (4) SDIO Card response with IORDY = 1 and MP = 0 (not SD memory, not combo card)

- (5) CMD3 and CMD7 to set in one active mode

- (6) CMD15 to put the card inactive

#### 6-1-2-2. SPI Mode Power-Up Transaction Sequence

- (1) CMD0 + CS = LOW

- (2) CMD5 (arg = 0)

- (3) SDIO Card response with OCR

- (4) CMD5 from host to set operation voltage using OCR

- (5) CMD15 to put the card inactive

#### 6-1-3. Operation Sequence

Table 6-3 lists the registers used to program the operation sequence. See the SDIO Registers section of the separate Host Interface Registers document for register programming information.

| Table 6-3 | SDIO Registers |

|-----------|----------------|

|-----------|----------------|

| Register       | Offset |  |  |  |  |

|----------------|--------|--|--|--|--|

| Host Interrupt | 0x107  |  |  |  |  |

| Card Status    | 0x120  |  |  |  |  |

Operation transaction sequences are as follows:

#### 6-1-3-1. SDIO Host Reads CIS Table Sequence

- (1) Check Card Status, Offset 0x120[2]. It is set by Card after CIS table is initialized.

- (2) HOST reads CIS Table using Function 0 address 8030\_807F and function 1 address 8080\_80FF.

### 6-1-3-2. SDIO Host Downloads Packet

- (1) Card sets Card Status, Offset 0x120[0].

- (2) Host Polls Dnld\_Card\_Rdy and IO\_Ready.

- (3) Host starts CMD53 block mode using function 1 with IO port address. CMD53 write clears Dnld\_Card\_Rdy.

- (4) Host sends the data in terms of predefined blocks. If BUSY, host delays the next block.

- (5) After CMD53 write completes, an interrupt CardInt is sent to firmware.

- (6) Firmware checks Host Interrupt Status, Offset 0x107[2] and Host Interrupt Status, Offset 0x107[0] registers. If Dnld\_CRC\_Err = 1, this packet has CRC error. If Dnld\_Restart = 1, firmware ignores this packet.

- (7) Back to the first step.

#### 6-1-3-3. SDIO Host Uploads Packet

- (1) Card sets Card Status, Offset 0x120[1].

- (2) UpId\_Card\_Rdy triggers an interrupt to SDIO HOST in the interrupt period.

- (3) SDIO HOST read to clear INT or write 0 to clear the interrupt.

- (4) SDIO HOST checks UpId\_Card\_Rdy and IO\_Ready.

- (5) HOST starts CMD53 read using function 1 with IO address with infinite block number or defined block number. CMD53 clears UpId\_Card\_Rdy bit.

- (6) After Host receives all data, HOST writes Abort using CMD52.

- (7) This terminate read operation. Card gets an interrupt with abort and with packet read, is complete.

- (8) Firmware reads interrupt, clears interrupt.

- (9) Firmware reads Host Interrupt Status, Offset 0x107[1]. If it is set by HOST, Firmware prepares to reissue this packet.

- (10) Back to the first step.

The SDIO HOST checks IO\_READY before starting a new CMD53. The SDIO target device can take a new SDIO HOST command only after the SDIO target device internal state machine is set back to IO\_READY state. Otherwise, the new CMD53 is ignored.

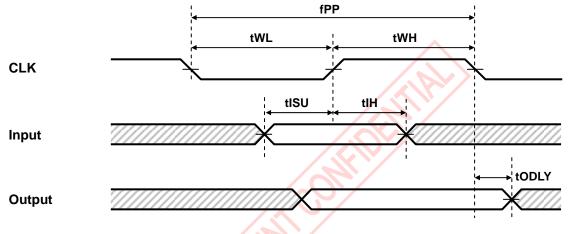

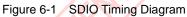

# 6-1-4. SDIO Timing

SDIO Timing specifications are shown in the followings.

| Symbol | Items             | Condition | Min  | Тур | Max | Unit |

|--------|-------------------|-----------|------|-----|-----|------|

| fPP    | CLK Frequency     | -         | 0    | -   | 50  | MHz  |

| tWL    | CLK Low Time      | -         | 11.1 | -   | -   | ns   |

| tWH    | CLK High Time     | -         | 11.1 | -   | -   | ns   |

| tISU   | Input Setup Time  | -         | 5    | -   | -   | ns   |

| tIH    | Input Hold Time   | -         | 5    | -   | -   | ns   |

| tODLY  | Output Delay Time | -         | 0    | -   | 15  | ns   |

Table 6-4 SDIO Timing Data

Note: The SDIO-SPI CS signal timing is identical to all other SDIO inputs.

#### 6-2. G-SPI Interface

MBH7WLZ16 supports a generic, half-duplex, DMA-assisted SPI host interface (G-SPI) that allows a host controller using a generic SPI bus protocol to access the WLAN device. The G-SPI interface contains interface circuitry between an external SPI bus and the internal shared bus.

The MBH7WLZ16 acts as the device on the SPI bus. The host unit can access the G-SPI registers directly and can access shared memory in MBH7WLZ16 through the use of BARs and DMA engine.

The SPI unit supports generic SPI interface protocols as detailed in the following sections. The design is capable of 50MHz operation. The interface supports the following functionally.

- SPI unit bus device operation.

- SPI unit register read / write.

- Interrupt generation to internal CPU.

- Interrupt generation to the SPI unit host.

- DMA to internal memories

- Wake interrupt to the Power Management Unit

MBH7WLZ16 G-SPI interface pins are powered from the VIO\_X1 voltage supply.

### 6-2-1. G-SPI Interface Functional Description

The G-SPI supports a variety of simple address/data protocols over a standard G-SPI physical bus. The protocols supported are differentiated by the number of address bits and data ordering.

Each transaction is initiated by assertion of the active low signal SCSn. Following the assertion of SCSn, the SDI input is latched with every positive edge of SCLK. When data is output, it is clocked out with the negative edge of SCLK. The clock input SCLK is low at the start and completion of a transaction.

### 6-2-1-1. Transaction Delays

The first block of data to be transferred is from host to the device. This block of data contains an address and read/write control. The MSB of the address is low for read operations and high for write operations.

# 6-2-1-1-1. Write Transaction Delay

For write transactions, the data phase of a transaction immediately follows the address phase of the transaction. There is no need to extend the low time of the clock between address and data or for the host to clock any dummy cycles.

# 6-2-1-1-2. Read Transaction Delay

There is a delay required between the end of the address phase on the bus and the start of the data phase of the transaction. This delay is shown as TDRR (time delay read register) and TDRP (time delay read port). This delay represents the time delay required for the device to prepare valid data to return to the host. This delay can be created in two different ways.

First, the read transaction delay is created by the host clocking a known number of dummy clock cycles to the device. The number of dummy clock cycles is specified in the Delay Read Register. There are two parameters in this parameter:

- Register read access

- Port read access

This mode is selected by setting the Delay Mode bit to 1 in the SPU Bus Mode, Offset 0x70[2].

Second, the delay is created by the host holding the clock signal low for a minimum period of time between the address and data phases. This mode is selected by setting the Delay Mode bit to 0 in the SPU Bus Mode, Offset 0x70[2].

During the data phase of a transaction, the host continues to provide clock pulse and either drives data on the SDI input or read data from the SDO output.

#### 6-2-1-2. Data Transfer

The host always accesses configuration registers in the G-SPI unit. To access internal memory space, some registers are defined as Port registers. When Port registers are accessed, the device reads or writes from internal memory space using the corresponding Base Address Register (BAR) and DMA engine.

Every transfer between host and device is a burst transfer (single address followed by multiple data). A transfer is terminated by the host after reading or writing the desired amount of data by de-asserting the SCSn input.

#### 6-2-1-2-1. Port Register Access

When the host system reads Port Registers, there is no limit to the burst length (other than the limit imposed by the valid address range of the internal bus). When the host system writes to Port Registers, the only condition on burst length is that the length be a multiple number of DWORDS.

Port Registers (I/O Port, Command Port, Data Port) are used to access internal 32-bit memory space and are always accessed on 32-bit boundaries. Each of these port registers has a corresponding BAR for reads and writes (acting as a pointer to the starting physical address location). Internal memory is also accessed only on 32-bit boundaries. This is accomplished by programming the corresponding BAR with 32-bit aligned values. During these accesses, the lower 16 bits are always presented on the bus first.

#### 6-2-1-2-1-1. Port Register Write Data

Write data to a Port Register is packed into sequential 32-bit memory locations starting at the location of the corresponding BAR. When reading from the Data and Command Ports of the device, the DMA engine continues to fill the FIFO whenever there is room for eight DWORDs (32-bits) of data. When writing data to the device, the de-assertion of SCSn input causes a flush to the write FIFO.

#### 6-2-1-2-1-2. Port Register Read Data

When reading data from the I/O Port of the device, it is selectable whether the DMA engine performs a single read or burst reads. Burst reads are treated like Data and Command Port reads. Single reads cause the DMA engine to perform a single DWORD access on the internal bus. A single read transaction must be terminated following the first or second 16-bit block of returned data.

#### 6-2-1-2-2. Configuration Register Access

When the host system accesses registers other than the Port Registers, the burst length must be limited to one 16-bit data transfer, or two 16-bit data transfers if the address is on a DWORD boundary. When a unit on the internal bus accesses G-SPI interface registers, the access must be a single DWORD access or smaller.

G-SPI interface registers, with the exception of Port Registers, can be read from or written to on 16-bit boundaries. Transactions can be terminated after a single 16-bit word is read or written.

#### 6-2-1-3. G-SPI Clock Frequency

The G-SPI clock frequency must not be greater than 2.5 times the internal bus clock frequency.

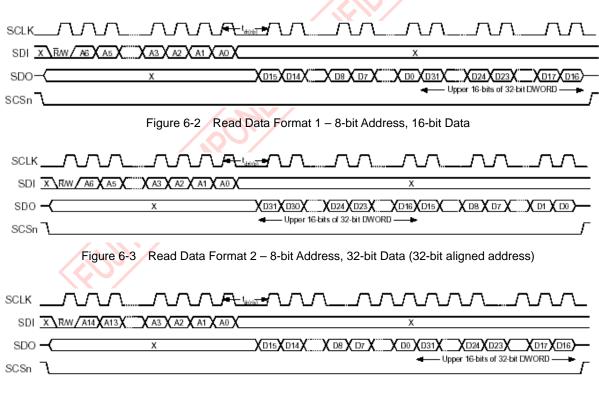

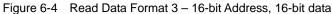

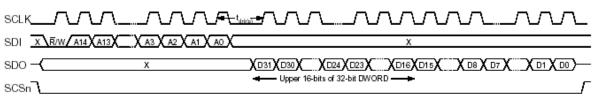

#### 6-2-1-4. Data Formats

There are a total of 16 valid data formats. The following nine data formats (shown below) are valid.

- All four data read formats in which the clock signal remains low during the delay between the address and data phase

- All four data write formats

- One data read format in which the clock signal toggles for a fixed number of cycles during the delay between the address and data phase

For each of the transaction types (read and write) there are two address lengths, either 8-bit or 16-bit. There are two data orderings for each address length.

Figure 6-2 through Figure 6-5 show the read data format when the Delay Method register control is 0. In this case, the 'tdr(r/p)' values represent a time delay between the last address bit in a given transaction and the first data bit for that same transaction. There are two different time delay values, reading from a G-SPI interface configuration register and reading from a G-SPI interface port register. Once the time delay value specified by the type of transaction has expired, valid data can be clocked from the device. The clock signal SCLK should remain low in Delay Method is 1, the data format is similar to the figures bellow with the exception that there are a fixed number of clock cycles between the address and data phase.

### 6-2-1-4-1. Programmable Clock Cycle Delay

6-2-1-4-1-1. Read Data Formats

# 6-2-1-4-1-2. Write Data Formats

| SDI X/RW\ A6 X A5 X X A3 X A2 X A1 X A0 X X XD15 XD14 X X D8 X D7 X X D0 XD31 X XD24 XD23 X XD17 XD16 X X       |

|-----------------------------------------------------------------------------------------------------------------|

| SDO - X                                                                                                         |

| SCSn                                                                                                            |

| Figure 6-6 Write Data Format 1 – 8-bit Address, 16-bit Data                                                     |

|                                                                                                                 |

| SDI X/RW\ A6 X A5 X XA3 X A2 X A1 X A0 X X X I31 X I30 X X I24 X I23 X X I16 X I16 X I16 X I17 X X I1 X I00 X X |

| sdo – ( x )                                                                                                     |

| SCSn Upper 16-bits of 32-bit DWORD —                                                                            |

| Figure 6-7 Write Data Format 2 – 8-bit Address, 32-bit Data (32-bit aligned address)                            |

|                                                                                                                 |

| SDI X/RW\A14XA13X XA3XA2XA1XA0XXXD15XD14X XD8XD7X XD0XD31X XD24XD23X XD17XD16XX                                 |

| spo – ( x )                                                                                                     |

| SCSn Upper 16-bits of 32-bit DWORD                                                                              |

| Figure 6-8 Write Data Format 3 – 16-bit Address, 16-bit Data                                                    |

|                                                                                                                 |

|                                                                                                                 |

| SDI X/RW\A14XA13X X A3 X A2 X A1 X A0 X X XD31XD30X XD24XD23X XD16XD15X XD8 X D7 X X D1 X D0 X X                |

| SDO — X<br>— Upper 16-bits of 32-bit DWORD — ►                                                                  |

| SCSn                                                                                                            |

| Figure 6-9 Write Data Format 4 – 16-bit Address, 32-bit Data (32-bit aligned address)                           |

| 6-2-1-4-2. Fixed Clock Cycle Delay                                                                              |

| 6-2-1-4-2-1. Example Read Data Format                                                                           |

| Figure 6-10 shows an example of one of the read data formats with a fixed clock cycle delay.                    |

|                                                                                                                 |

|                                                                                                                 |

| SDO - X X 1' XD15XD14X X D8 X D7 X X D0 XD31X XD24 XD23X XD17 XD16}-<br>- Upper 16-bits of 32-bit DWORD         |

| scsn \                                                                                                          |

Figure 6-10 Read Data Format – 16-bit Address, 16-bit Data (fixed clock delay)

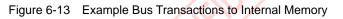

#### 6-2-1-5. Example Transactions

The tables and figures below show some example host transactions on the G-SPI interface bus. Table 6-5 and Table 6-6 show memory ranges and data for G-SPI interface register space and internal memory space.

From the Host System, G-SPI interface registers can be accessed on 16-bit boundaries with the exception of the Port Registers. From the internal bus, registers are always accessed on 32-bit boundaries.

Table 6-5 shows a portion of the G-SPI interface configuration register space. Register addresses are shown from both the Host System and the internal bus. Example data which is used in Figure 6-11, is shown stored in the registers.

Table 6-6 shows a portion of the SQU memory on the internal bus, along with example data used in Figure 6-11.

For these examples, it is assumed all base address registers contain the value 0xC000\_1000. Address and data values in the example figures are in hexidecimal.

An "x" represents an undefined (don't care) value. A "z" re presents a high impedance state.

| Bi    | Bits         |               | ts    | Internal Address |

|-------|--------------|---------------|-------|------------------|

| 31    | 16           | 15 0          |       |                  |

| Addre | ess from Hos | t (and stored | data) |                  |

| 0x0   | 042          | 0x0           | 040   | 0x8000 0040      |

| 0x0   | 0x0046       |               | 044   | 0x8000 0044      |

| 0x0   | 04A          | 0x0048        |       | 0x8000 0048      |

| 0x0   | 04E          | 0x004C        |       | 0x8000 004C      |

| 0x0   | 052          | 0x0050        |       | 0x8000 0050      |

| 0x0   | 0x0056       |               | 054   | 0x8000 0054      |

| 0x0   | 0x005A       |               | 058   | 0x8000 0058      |

| 0x0   | 05E          | 0x00          | 05C   | 0x8000 005C      |

Table 6-5 G-SPI Interface Register Memory Space

#### Table 6-6 Internal SQU memory Space

| Bits   | Internal Address |          |     |             |

|--------|------------------|----------|-----|-------------|

|        |                  | Bi<br>15 |     |             |

| <br>31 | 16               | -        | 0   |             |

|        | Stored           | i Data   |     |             |

| 0x1002 |                  | 0x1      | 000 | 0x8000 1000 |

| 0x1006 |                  | 0x1      | 004 | 0x8000 1004 |

| 0x100A |                  | 0x1      | 800 | 0x8000 1008 |

| 0x100E |                  | 0x10     | 00C | 0x8000 100C |

| 0x1012 |                  | 0x1010   |     | 0x8000 1010 |

| 0x1016 |                  | 0x1014   |     | 0x8000 1014 |

| 0x101A |                  | 0x1018   |     | 0x8000 1018 |

| 0x101E |                  | 0x10     | )1C | 0x8000 101C |

|      |   | Addr | Data |      |   |    |   |   |   |

|------|---|------|------|------|---|----|---|---|---|

| SDI  | х | 0042 | х    | х    | х | х  | х | Х | Х |

| SDO  | Z | х    | 0042 | Z    | Z | Z  | Z | Z | Z |

| SCSn |   |      |      |      |   |    |   |   |   |

| _    |   |      |      |      |   |    |   |   |   |

| SDI  | х | 0040 | х    | х    | х | Х  | х | Х | х |

| SDO  | Z | х    | 0040 | 0042 | Z | Z  | Z | Z | z |

| SCSn |   |      |      |      |   |    |   |   |   |

|      |   |      |      |      |   |    |   |   |   |

| SDI  | х | 8044 | 0044 | х    | х | х  | х | х | х |

| SDO  | Z | х    | х    | Z    | Z | Z  | Z | Z | Z |

| SCSn |   |      |      |      |   |    |   |   |   |

|      |   |      |      |      |   |    |   |   |   |

| SDI  | х | 8044 | 0044 | 0046 | х | х  | х | x | х |

| SDO  | Z | х    | х    | х    | х | х  | x | x | Z |

| SCSn |   |      |      |      |   | 10 |   |   |   |

|      |   |      |      |      |   |    |   |   |   |

Figure 6-11 Example Bus Transactions to Register Space – 16-bit Address and 16-bit Data

|      |   | Addr |      |      | CY | Data |   |   |   |

|------|---|------|------|------|----|------|---|---|---|

| SDI  | х | 0040 | х    | X    | x  | х    | х | х | х |

| SDO  | z | х    | 0042 | Z    | z  | Z    | Z | Z | Z |

| SCSn |   |      | 60   |      |    |      |   |   |   |

| SDI  | х | 0040 | x    | х    | х  | х    | х | х | х |

| SDO  | z | x    | 0042 | 0040 | Z  | Z    | Z | Z | Z |

| SCSn |   |      |      |      |    |      |   |   |   |

| SDI_ | x | 8044 | 0046 | x    | х  | х    | х | х | х |

| SDO  | z | х    | х    | Z    | Z  | Z    | Z | Z | Z |

| SCSn |   |      |      |      |    |      |   |   |   |

| SDI_ | х | 8044 | 0046 | 0044 | х  | х    | х | х | х |

| SDO  | z | х    | х    | х    | х  | х    | х | х | Z |

| SCSn |   |      |      |      |    |      |   |   |   |

Figure 6-12 Example Bus Transactions to Register Space – Data Formats 7 and 11

|      |   | Addr |      |      |      | Data |      |      |   |  |  |

|------|---|------|------|------|------|------|------|------|---|--|--|

| SDI  | х | 0024 | х    | х    | х    | х    | х    | х    | х |  |  |

| SDO  | Z | Х    | 1000 | 1002 | Z    | Z    | Z    | Z    | Z |  |  |

| SCSn |   |      |      |      |      |      |      |      |   |  |  |

| SDI  | х | 0024 | х    | х    | х    | х    | х    | х    | х |  |  |

| SDO  | Z | Х    | 1000 | 1002 | 1004 | 1006 | 1008 | 100A | Z |  |  |

| SCSn |   |      |      |      |      |      |      |      |   |  |  |

|      |   |      |      |      |      |      |      |      |   |  |  |

| SDI  | х | 8024 | 1000 | 1002 | х    | х    | х    | х    | х |  |  |

| SDO  | z | Х    | х    | Z    | Z    | Z    | Z    | Z    | Z |  |  |

| SCSn |   |      |      |      |      |      |      | •    |   |  |  |

|      |   |      |      |      |      |      |      |      |   |  |  |

| SDI  | х | 8024 | 1000 | 0002 | 0004 | 0006 | 0008 | 000A | х |  |  |

| SDO  | z | х    | х    | х    | х    | х    | x    | x    | Z |  |  |

| SCSn |   |      |      |      |      |      |      |      |   |  |  |

FUIDICOMPONENT

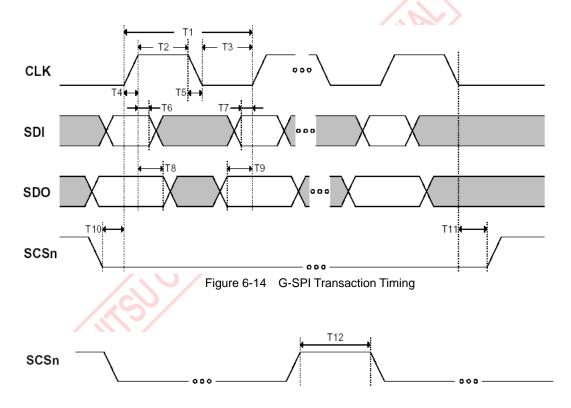

# 6-2-2. G-SPI Timing

G-SPI Timing specifications are shown in the followings.

| Symbol | Parameter              | Min | Тур | Max      | Unit |

|--------|------------------------|-----|-----|----------|------|

| T1     | Clock Period           | 20  |     |          | ns   |

| T2     | Clock High             | 5   |     |          | ns   |

| Т3     | Clock Low              | 9   |     |          | ns   |

| T4     | Clock Rise Time        |     |     | 1        | ns   |

| T5     | Clock Fall Time        |     |     | 1        | ns   |

| T6     | SDI Hold Time          | 2.5 |     |          | ns   |

| T7     | SDI Setup Time         | 2.5 |     |          | ns   |

| T8     | SDIO Hold Time         | 5   |     |          | ns   |

| Т9     | SDIO Setup Time        | 1   |     |          | ns   |

| T10    | SCSn Fall to Clock     | 5   |     |          | ns   |

| T11    | Clock to SCSn Rise     | 0   |     |          | ns   |

| T12    | SCSn Rise to SCSn Fall | 400 |     | <b>^</b> | ns   |

Table 6-7 G-SPI Timing Data

Figure 6-15 G-SPI Inter-Transaction Timing

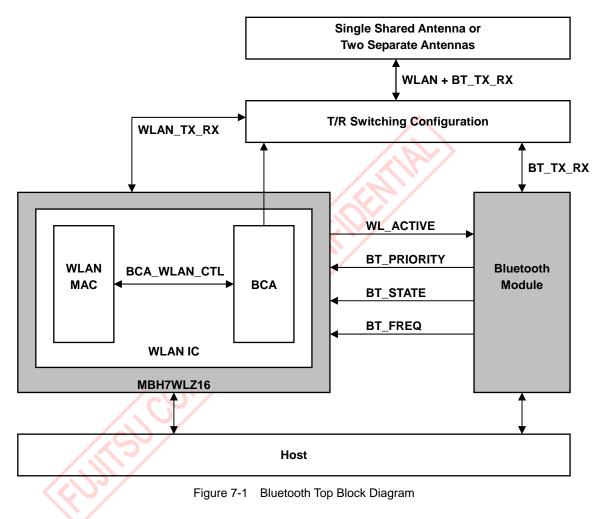

## 7. Bluetooth Coexistence

MBH7WLZ16 supports coexistence capability with co-located Bluetooth devices.

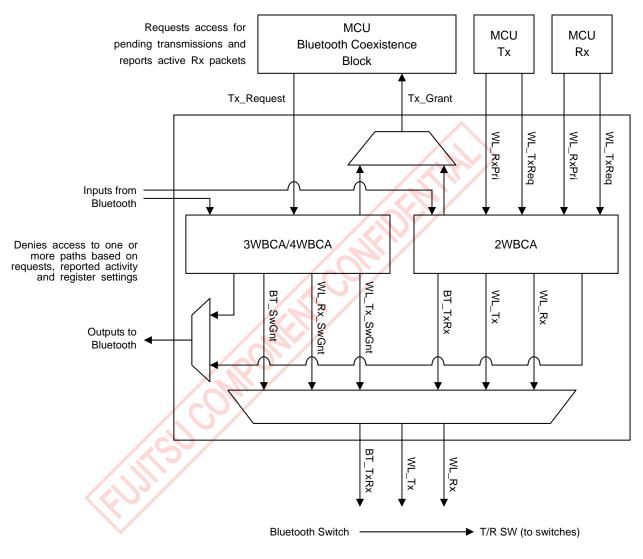

- There are three Bluetooth Coexistence Arbitration (BCA) units in MBH7WLZ16:

- 2-Wire Bluetooth Coexistence Arbitration (2WBCA) scheme

- 3-Wire Bluetooth Coexistence Arbitration (3WBCA) scheme

- 4-Wire Bluetooth Coexistence Arbitration (4WBCA) scheme

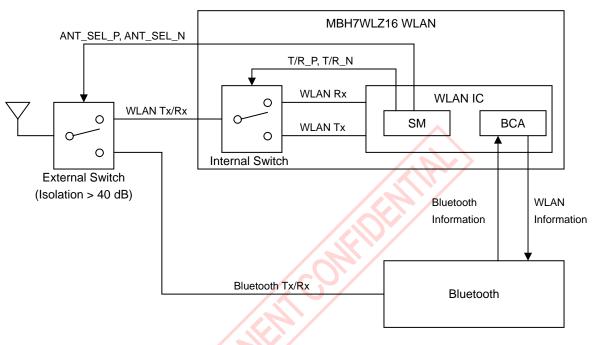

Only one of the BCA units can be used at a time. In addition, MBH7WLZ16 contains a Switch Module (SM) that controls antenna switching for both single antenna and dual antenna applications.

# 7-1. System Level Configuration

Hardware configurability enables the following system-level configuration options:

- Bluetooth v1.1 or Bluetooth v1.2 Adaptive Frequency Hopping (AFH)

- QoS-aware 2-wire coexistence signaling interface or 4-wire coexistence signaling interface

- Single shared antenna or dual antenna

- For single antenna system, dual 2-port T/R switching configuration

- Configurable timing on coexistence signaling interface and switch control interface

- Future-proofed firmware programmable and system-configurable QoS classification and prioritization

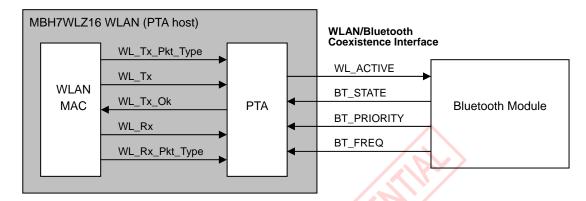

# 7-2. WLAN/Bluetooth Channel Information Exchange

Since Bluetooth and 802.11b/g WLAN use the same 2.4 GHz frequency band, each can cause interference with the other. The level of interference depends on the respective frequency channel used by Bluetooth and WLAN (other factors can impact interference, like Tx power and Rx sensitivity of the device).

In a system with both Bluetooth and WLAN, the common host receives information about WLAN channel usage and passes this information to the Bluetooth device. For Bluetooth v1.2 devices with AFH enabled, the Bluetooth device can block channel usage that overlaps the WLAN channel in use.

When the Bluetooth device avoids all channels used by the WLAN, the impact of interference is greatly reduced, but not completely eliminated. For Bluetooth v1.1 devices, the Bluetooth device cannot block WLAN channel usage and an active BCA scheme at the MAC levels is required. The BCA scheme can also be used with Bluetooth v1.2 devices to further reduce the impact of interference to a minimum.

# 7-2-1. Dual/Single Antenna Support

All the arbitration units support dual and single antenna configurations.

# 7-2-1-1. Dual Antenna Configuration

In dual antenna configurations, both WLAN and Bluetooth have their own dedicated antennas. In this case, the BCA allows simultaneous WLAN and Bluetooth transactions, resulting in higher WLAN/Bluetooth network performance. Figure 7-2 shows the Dual Antenna Configuration.

Figure 7-2 Dual Antenna Configuration

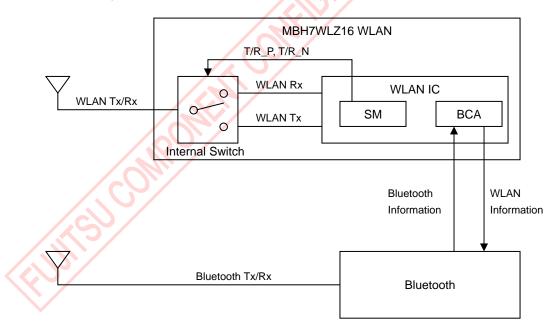

# 7-2-1-2. Single Antenna Configuration

In single antenna configurations, both WLAN and Bluetooth share one antenna. In this case, the BCA must ensure that only one device is allowed to use the antenna. A single antenna configuration has an advantage of lower cost and board space saving, compared to the dual antenna configuration.

The external RF switch for the single antenna needs additional control signals for switch control. This is accomplished by Switch Module (SM) logic in MBH7WLZ16. Figure 7-3 shows the Single Antenna Configuration with 2-way switch.

Figure 7-3 Single Antenna Configuration with 2-way Switch

# 7-3. 2-Wire BCA

The 2WBCA interface decides which device has primary access to the shared wireless medium according to the 2WBCA coexistence scheme. The 2WBCA interface makes its decision based on input signals from the Bluetooth device, input signals from the 802.11 MAC device, and MAC register settings. The input signals from the 802.11 and Bluetooth device report activity or priority for their respective devices. The 2WBCA interface module compares any conflicting traffic based on a programmable table in the MAC registers.

Figure 7-4 2WBCA Block Diagram

#### 7-3-1. 2-Wire BCA Arbitration Tables

The arbitration scheme is as follows:

- WLAN high-priority packets have priority over all Bluetooth packets. Bluetooth high-priority packets have priority over WLAN low-priority packets.

- When the Bluetooth priority signal is asserted, the arbiter checks if the WLAN has a Tx or Rx request. If the WLAN requests during this time, the arbiter makes an arbitration decision based on the arbiter decision table. Typically, for the Bluetooth device, once the arbiter allows it to transmit, the Bluetooth does not stop transmitting until the transmitting packet completes. For this reason, if a higher priority WLAN request enters while the Bluetooth is transmitting, the arbiter allows the Bluetooth to complete transmission before granting access to the WLAN.

- For WLAN requests, the arbiter has no WLAN arbitration window, but the arbiter may stop the WLAN while the WLAN is in the middle of packet transmission. Since there is no WLAN arbitration window, the WLAN is granted access immediately if there is no Bluetooth request at that time. Except for WLAN high-priority packets, there is no guarantee that WLAN can transmit or receive (for single antenna case) the entire packet. The arbiter can stop the WLAN from transmitting or receiving (for single antenna case) in the middle of the packet if there is a new Bluetooth request, and the new arbiter decision is in favor of the Bluetooth packet. This approach optimizes the performance of Bluetooth voice applications, at the expense of WLAN performance.

| WLAN Tx<br>Request | WLAN Tx<br>Priority | WLAN Rx<br>Request | WLAN Rx<br>Priority | Bluetooth<br>Priority | Result                                                   |

|--------------------|---------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------|

| 0                  | 0                   | 1                  | 0                   | 1                     | Stop Low Priority WLAN Rx<br>High Priority Bluetooth OK  |

| 0                  | 0                   | 1                  | 1                   | 1                     | High Priority WLAN Rx OK<br>Stop High Priority Bluetooth |

| 1                  | 0                   | 0                  | 0                   | 1                     | Stop Low Priority WLAN Tx<br>High Priority Bluetooth OK  |

| 1                  | 1                   | 0                  | 0                   | 1                     | High Priority WLAN Tx OK<br>Stop High Priority Bluetooth |

Table 7-1 Single Antenna Default Arbitration Table

| Table 7-2 | Dual A | Antenna Defau | It Arbitration I | able     |

|-----------|--------|---------------|------------------|----------|

|           | Γv     |               |                  | Pluotoot |

| WLAN Tx<br>Request | WLAN Tx<br>Priority | WLAN Rx<br>Request | WLAN Rx<br>Priority | Bluetooth<br>Priority | Result                                                   |

|--------------------|---------------------|--------------------|---------------------|-----------------------|----------------------------------------------------------|

| 0                  | 0                   | 1                  | 0                   | 1                     | Low Priority WLAN Rx OK<br>High Priority Bluetooth OK    |

| 0                  | 0                   | 1                  | 1                   | 1                     | High Priority WLAN Rx OK<br>High Priority Bluetooth OK   |